Advanced Computer Architecture II - Interconnect Networks Overview

This set of lecture notes covers the fundamentals of interconnection networks in advanced computer architecture, focusing on topics such as network topologies, routing, flow control, and router microarchitecture. The importance of efficient interconnection network design in maximizing information transfer within computational systems is highlighted, with insights into application, technology, and performance considerations.

Download Presentation

Please find below an Image/Link to download the presentation.

The content on the website is provided AS IS for your information and personal use only. It may not be sold, licensed, or shared on other websites without obtaining consent from the author.If you encounter any issues during the download, it is possible that the publisher has removed the file from their server.

You are allowed to download the files provided on this website for personal or commercial use, subject to the condition that they are used lawfully. All files are the property of their respective owners.

The content on the website is provided AS IS for your information and personal use only. It may not be sold, licensed, or shared on other websites without obtaining consent from the author.

E N D

Presentation Transcript

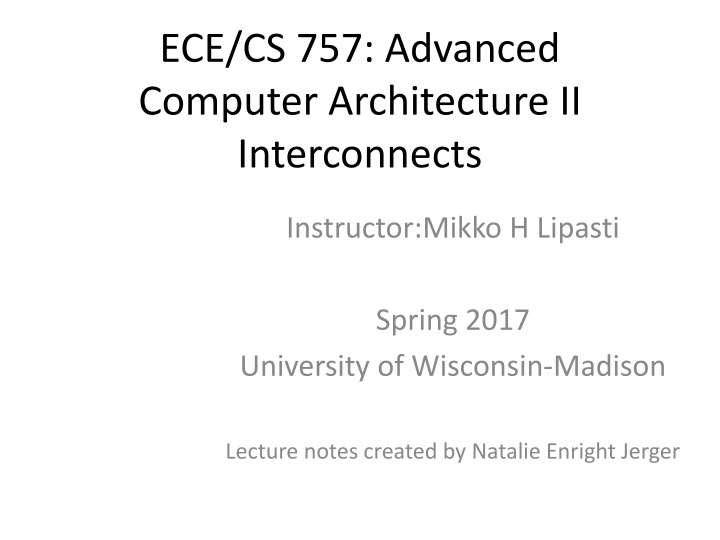

ECE/CS 757: Advanced Computer Architecture II Interconnects Instructor:Mikko H Lipasti Spring 2017 University of Wisconsin-Madison Lecture notes created by Natalie Enright Jerger

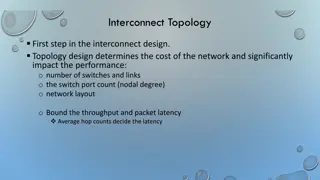

Lecture Outline Introduction to Networks Network Topologies Network Routing Network Flow Control Router Microarchitecture Mikko Lipasti-University of Wisconsin 2

What is an Interconnection Network? Application Algorithm Programming Language Operating System Instruction Set Architecture Microarchitecture Register Transfer Level Circuits Devices Technology Computer Architecture Logic Mem Logic Mem Communication Logic Mem Logic Mem ECE 1749H: Interconnection Networks (Enright Jerger) Spring 2014 3

What is an Interconnection Network? Application Algorithm Programming Language Operating System Instruction Set Architecture Microarchitecture Register Transfer Level Circuits Devices Technology Computer Architecture Logic Mem Logic Mem Dedicated Channels Logic Mem Logic Mem Application: Ideally wants low-latency, high-bandwidth, dedicated channels between logic and memory Technology: Dedicated channels too expensive in terms of area and power ECE 1749H: Interconnection Networks (Enright Jerger) Spring 2014 4

What is an Interconnection Network? Application Algorithm Programming Language Operating System Instruction Set Architecture Microarchitecture Register Transfer Level Circuits Devices Technology Computer Architecture Logic Mem Logic Mem Interconnection Network Logic Mem Logic Mem An Interconnection Network is a programmable system that transports data between terminals Technology: Interconnection network helps efficiently utilize scarce resources Application: Managing communication can be critical to Spring 2014 performance ECE 1749H: Interconnection Networks (Enright Jerger) 5

Interconnection Networks Introduction Interconnection networks should be designed to transfer the maximum amount of information within the least amount of time (and cost, power constraints) so as not to bottleneck the system ECE 1749H: Interconnection Networks (Enright Jerger) Spring 2014 6

Types of Interconnection Networks Interconnection networks can be grouped into four domains Depending on number and proximity of devices to be connected On-Chip Networks (OCNs or NoCs) Devices include microarchitectural elements (functional units, register files), caches, directories, processors Current/Future systems: dozens, hundreds of devices Ex: Intel TeraFLOPS research prototypes 80 cores Intel Single-chip Cloud Computer 48 cores Proximity: millimeters ECE 1749H: Interconnection Networks (Enright Jerger) Spring 2014 7

Types of Interconnection Networks (2) System/Storage Area Networks (SANs) Multiprocessor and multicomputer systems Interprocessor and processor-memory interconnections Server and data center environments Storage and I/O components Hundreds to thousands of devices interconnected IBM Blue Gene/L supercomputer (64K nodes, each with 2 processors) Maximum interconnect distance: tens of meters (typical) to a few hundred meters Examples (standards and proprietary) InfiniBand, Myrinet, Quadrics, Advanced Switching Interconnect ECE 1749H: Interconnection Networks (Enright Jerger) Spring 2014 8

Types of Interconnection Networks (3) Local Area Networks (LANs) Interconnect autonomous computer systems Machine room or throughout a building or campus Hundreds of devices interconnected (1,000s with bridging) Maximum interconnect distance few kilometers to few tens of kilometers Example (most popular): Ethernet, with 10 Gbps over 40Km Wide Area Networks (WANs) Interconnect systems distributed across globe Internetworking support required Many millions of devices interconnected Max distance: many thousands of kilometers Example: ATM (asynchronous transfer mode) ECE 1749H: Interconnection Networks (Enright Jerger) Spring 2014 9

Interconnection Network Domains Wide Area Networks 106 Distance (meters) Metropolita n Area Networks 103 Local Area Networks System/Storage Area Networks 100 10-3 1 10 100 1,000 10,000 >100,000 Number of devices interconnected ECE 1749H: Interconnection Networks (Enright Jerger) Spring 2014 10 Slide courtesy Timothy Mark Pinkston and Jos Duato

Interconnection Network Domains Wide Area Networks 106 Distance (meters) Metropolitan Area Networks 103 Local Area Networks System/Storage Area Networks 100 On-Chip Interconnection Networks/Networks-on- Chip 10-3 1 10 100 1,000 10,000 >100,000 Number of devices interconnected ECE 1749H: Interconnection Networks (Enright Jerger) Spring 2014 11 Slide courtesy Timothy Mark Pinkston and Jos Duato

Why Study Networks on Chip? ECE 1749H: Interconnection Networks (Enright Jerger) Spring 2014 12

Why Study On-Chip Networks? ECE 1749H: Interconnection Networks (Enright Jerger) Spring 2014 13

Example of Multi- and Many-Core Architectures ECE 1749H: Interconnection Networks (Enright Jerger) Spring 2014 14

Why study interconnects? They provide external connectivity from system to outside world Also, connectivity within a single computer system at many levels I/O units, boards, chips, modules and blocks inside chips Trends: high demand on communication bandwidth increased computing power and storage capacity switched networks are replacing buses Computer architects/engineers must understand interconnect problems and solutions in order to more effectively design and evaluate systems ECE 1749H: Interconnection Networks (Enright Jerger) Slide courtesy Timothy Mark Pinkston and Jos Duato Spring 2014 15

On-Chip Networks (OCN or NoCs) Why On-Chip Network? Ad-hoc wiring does not scale beyond a small number of cores Prohibitive area Long latency OCN offers scalability efficient multiplexing of communication often modular in nature (ease verification) ECE 1749H: Interconnection Networks (Enright Jerger) Spring 2014 16

Differences between on-chip and off- chip networks Significant research in multi-chassis interconnection networks (off-chip) Supercomputers Clusters of workstations Internet routers Leverage research and insight but Constraints are different New opportunities ECE 1749H: Interconnection Networks (Enright Jerger) Spring 2014 17

Off-chip vs. on-chip Off-chip: I/O bottlenecks Pin-limited bandwidth Inherent overheads of off-chip I/O transmission On-chip Wiring constraints Metal layer limitations Horizontal and vertical layout Short, fixed length Repeater insertion limits routing of wires Avoid routing over dense logic Impact wiring density ECE 1749H: Interconnection Spring 2014 18 Networks (Enright Jerger)

Off-Chip vs On-Chip On-Chip Power Consume 10-15% or more of die power budget Latency Different order of magnitude Routers consume significant fraction of latency ECE 1749H: Interconnection Networks (Enright Jerger) Spring 2014 19

New opportunities Abundant wiring Change in relative cost of wires and buffers Many short flits Tightly integrated into system Not commodity fully customized design Allows for optimization with uncore Cache coherence Emerging technology Optics 3D ECE 1749H: Interconnection Networks (Enright Jerger) Spring 2014 20

On-Chip Network Evolution Ad hoc wiring Small number of nodes Buses and Crossbars Simplest variant of on-chip networks Low core counts Like traditional multiprocessors Bus traffic quickly saturates with a modest number of cores Crossbars: higher bandwidth Poor area and power scaling ECE 1749H: Interconnection Networks (Enright Jerger) Spring 2014 21

Multicore Examples (1) 0 1 2 3 4 5 0 1 XBAR 2 3 4 5 Sun Niagara Niagara 2: 8x9 crossbar (area ~= core) Rock: Hierarchical crossbar (5x5 crossbar connecting clusters of 4 cores) Spring 2014 ECE 1749H: Interconnection Networks (Enright Jerger) 22

Multicore Examples (2) IBM Cell Element Interconnect Bus 12 elements 4 unidirectional rings 16 Bytes wide Operates at 1.6 GHz RING IBM Cell ECE 1749H: Interconnection Networks (Enright Jerger) Spring 2014 23

Many Core Example Intel TeraFLOPS 80 core prototype 5 GHz Each tile: Processing engine + on-chip network router 2D MESH Spring 2014 ECE 1749H: Interconnection Networks (Enright Jerger)

Many-Core Example (2): Intel SCC Intel s Single-chip Cloud Computer (SCC) uses a 2D mesh with state of the art routers ECE 1749H: Interconnection Networks (Enright Jerger) Spring 2014 25

Performance and Cost Latency (sec) Zero load latency Offered Traffic (bits/sec) throughput Saturation Performance: latency and throughput Cost: area and power ECE 1749H: Interconnection Networks (Enright Jerger) Spring 2014 26

Lecture Outline Introduction to Networks Network Topologies Network Routing Network Flow Control Router Microarchitecture Mikko Lipasti-University of Wisconsin 27

Readings Read: [18] N. Enright Jerger, L.-S. Pei, On-Chip Networks, Synthesis Lectures on Computer Architecture, http://www.morganclaypool.com/doi/abs/10.2200/S 00209ED1V01Y200907CAC008 Review: [19] D. Wentzlaff, P. Griffin, H. Hoffmann, L. Bao, B. Edwards, C. Ramey, M. Mattina, C.-C. Miao, J. F. B. III, and A. Agarwal. On-Chip Interconnection Architecture of the Tile Processor. IEEE Micro, vol. 27, no. 5, pp. 15-31, 2007 Mikko Lipasti-University of Wisconsin 28

![❤Book⚡[PDF]✔ The Apollo Guidance Computer: Architecture and Operation (Springer](/thumb/21611/book-pdf-the-apollo-guidance-computer-architecture-and-operation-springer.jpg)