ARM Assembly Language Programming & Architecture

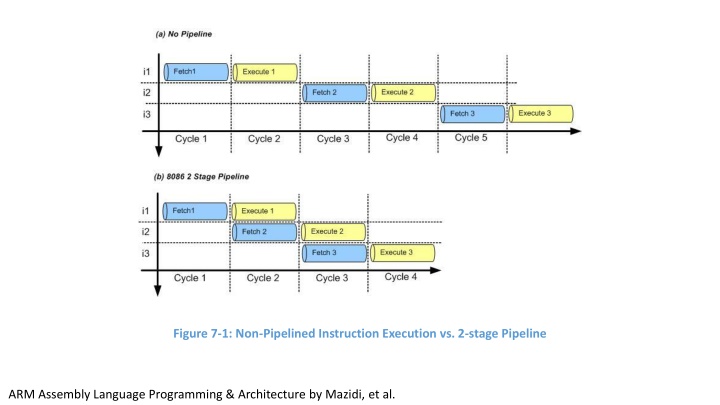

This content showcases figures illustrating non-pipelined instruction execution, 2-stage pipeline, 5-stage pipeline in ARM9, superscalar CPUs, CPU instruction execution, and the top-level diagram of the ARM Cortex A9 processor from the book "ARM Assembly Language Programming & Architecture" by Mazidi et al. These visuals provide insights into the evolution of processor architectures and the impact on instruction execution in ARM assembly language programming.

Download Presentation

Please find below an Image/Link to download the presentation.

The content on the website is provided AS IS for your information and personal use only. It may not be sold, licensed, or shared on other websites without obtaining consent from the author.If you encounter any issues during the download, it is possible that the publisher has removed the file from their server.

You are allowed to download the files provided on this website for personal or commercial use, subject to the condition that they are used lawfully. All files are the property of their respective owners.

The content on the website is provided AS IS for your information and personal use only. It may not be sold, licensed, or shared on other websites without obtaining consent from the author.

E N D

Presentation Transcript

Figure 7-1: Non-Pipelined Instruction Execution vs. 2-stage Pipeline ARM Assembly Language Programming & Architecture by Mazidi, et al.

Figure 7- 2: 5-Stage Pipeline in ARM9 ARM Assembly Language Programming & Architecture by Mazidi, et al.

Figure 7- 3: Superscalar CPUs ARM Assembly Language Programming & Architecture by Mazidi, et al.

Figure 7- 4: CPU Instruction Execution ARM Assembly Language Programming & Architecture by Mazidi, et al.

Figure 7- 5: Top-level diagram of the ARM Cortex A9 processor ARM Assembly Language Programming & Architecture by Mazidi, et al.