COGRE Architecture for Area Minimization in Logic Cells

Explore the COGRE configuration memory reduced architecture for area minimization in logic cells, a paper by Yasuhiro Okamoto et al. from Kumamoto University, Japan. Learn about NPN-Equivalence classes, high appearance ratio of NPN-equivalents, and the characteristics of COGRE architecture.

Download Presentation

Please find below an Image/Link to download the presentation.

The content on the website is provided AS IS for your information and personal use only. It may not be sold, licensed, or shared on other websites without obtaining consent from the author. If you encounter any issues during the download, it is possible that the publisher has removed the file from their server.

You are allowed to download the files provided on this website for personal or commercial use, subject to the condition that they are used lawfully. All files are the property of their respective owners.

The content on the website is provided AS IS for your information and personal use only. It may not be sold, licensed, or shared on other websites without obtaining consent from the author.

E N D

Presentation Transcript

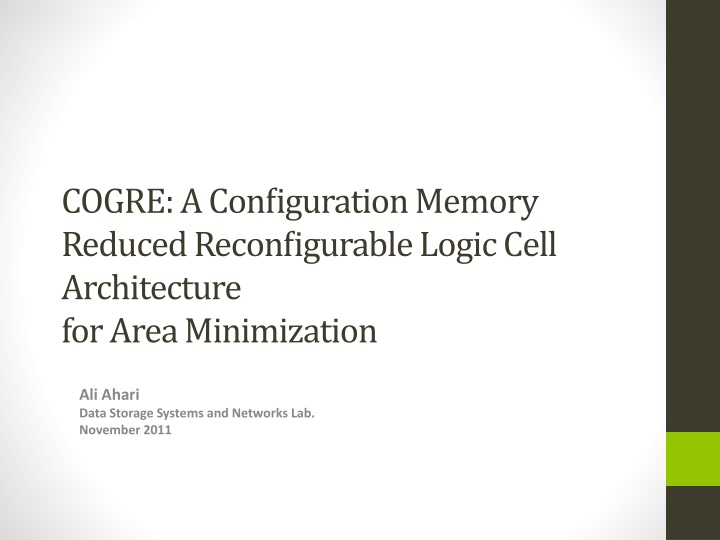

COGRE: A Configuration Memory Reduced Reconfigurable Logic Cell Architecture for Area Minimization Ali Ahari Data Storage Systems and Networks Lab. November 2011

Outline Introduction Ideas Evaluation Conclusion

Introduction We are going to talk about COGRE a paper by Yasuhiro Okamoto et al. from Kumamoto University, Japan which was appeared on FPL 2010. It is an alternative architecture for LUTs.

Main Ideas A lot of redundancy in configuration mem. High appearance ratio of NPN-equivalence logics New BLE structure Reducing configuration memory bits Is not a new story! Just placement and routing is done!

NPN-Equivalence Class Definition: Given two functions F and G , if function F can be derived from G by negating (N) and/or permuting (P) some inputs and/or by negating (N) the output, functions F and G are NPN equivalent and belong to the same NPN-equivalence class. Example: F = A + B C G = B ( A + C )

High Appearance Ratio of NPN- equivalents 2( N +1) *N ! distinct functions have same NPN- equivalence class (N-input function) 20 largest MCNC circuits 88.3% of the 4-input logic functions by only 6 out of the 222 NPN-equivalence classes

Characteristics 5-COGRE : 93.4% functionality 4-LUT 8 vs 16 configuration bits Some 5 input functionality. Constant assignment 6-COGRE : 50.6% functionality 6-LUT 11 vs 32 configuration bits

Evaluation technology mapping priority-cut-based LUT mapper Not all functions A special libraray

Evaluation(Cont.) Just combinational delay

Summary of evaluation Parameters 6-COGRE vs 6-LUT 5-COGRE vs 5-LUT 5-COGRE vs 4-LUT Logic Area 46.3% 32.6% 10.0% Routing Area 9.66% 11.8% 12.7% Total Number of Routing Tracks 4.12% 10.0% 4.83% Total Number of CMBs 32.1% 13.2% 1.95% Critical Path Delay 6.96% 5.29% 2.72% : improvement : degradation

Total Number of Routing Tracks

Total Number of Configuration Memory Bits

Conclusion A good opportunity for improve logic efficiency Does not cover all logics Better Logic Area vs. Worse Routing Total Area???

Future Work Effectiveness of cluster architecture and BLE structure Combination of COGREs and LUTs Heterogeneous COGRE cluster