CXL Resources Modeling and System Composition

Explore the modeling of CXL resources including CPU, DRAM, ports, switches, and logical devices in a composable system. Witness the evolution of Type 3 SLD to MLD memory configurations with potential extensions for enhanced performance.

Download Presentation

Please find below an Image/Link to download the presentation.

The content on the website is provided AS IS for your information and personal use only. It may not be sold, licensed, or shared on other websites without obtaining consent from the author. If you encounter any issues during the download, it is possible that the publisher has removed the file from their server.

You are allowed to download the files provided on this website for personal or commercial use, subject to the condition that they are used lawfully. All files are the property of their respective owners.

The content on the website is provided AS IS for your information and personal use only. It may not be sold, licensed, or shared on other websites without obtaining consent from the author.

E N D

Presentation Transcript

Redfish modeling of CXL resources - Christian, Michele, Atul

Composable system example: physical resources Composable module 1 1 CPU Unit 1 DRAM Unit CPU DRAM DRAM Composable Module 1 Composable Module 2 Composable module 2 1 DRAM Unit 1 CXL Port Models CXL Type-3 SLD CXL link CXL link CXL Switch CXL Switch 2 Ports

Composable system example: composed system Composable module 1 1 CPU Unit 1 DRAM Unit Composable module 2 1 DRAM Unit 1 CXL Port Models CXL Type-3 SLD CXL Switch 2 Ports Composed System S1 1 CPU 1 Local DRAM 1 Remote DRAM Composed System S1 CPU DRAM DRAM Composable Module 1 Composable Module 2 CXL link CXL link CXL Switch

Composable module 1 Root Chassis Systems Chassis1 CM1 Processors Memory Memory Domains Fabric adapter CPU1 DIMM1 Domain1 Adapter 1 Memory Chunk Ports Chunk1 1

Type 3 SLD Memory Composable Module 2 Chassis PCIe Devices 1 1 1 PCIe Devices Devices PCIe Chassis2 PCIe PCIe Functions Functions CXL Logical Devices 1 Fabric Adapters 1 Memory Domains 1 1 Memory Memory Chunks Ports DIMM1 1 Chunk1 Should Chunk1 object exist before binding to host is done?

Potential extension of Type 3 SLD to Type 3 MLD memory Chassis Chassis2 PCIe Devices Devices Devices 1 PCIe PCIe Memory Domains Fabric Adapters 1 1 PCIe Functions 2 1 CXL Logical Devices 2 1 Ports 1 Memory DIMM1 Memory Chunks Chunk2 Chunk1

Time T0 : no binding yet, between Composable Module 1 and Composable Module 2 Root Chassis Systems CM1 PCIe Devices 1 Chassis1 Fabrics Processors CXL Memory Domains 1 PCIe Fabric adapter Adapter 1 MemoryD omains CPU1 Fabric Adapters 1 Functions Memory CXL Logical Devices 1 DIMM1 Domain1 Switches 1 CXL Ports Memory Chunk Memory Memory Chunks Ports Ports U1 1 DIMM1 D1 1 Chunk1 Chunk1

Time T1 : post-binding between Composable Module 1 and 2 Root Systems CM1 Chassis PCIe Devices 1 Chassis1 Fabrics CXL Fabric adapter Adapter 1 Memory Domains Memory Domains 1 Processors PCIe Functions Fabric Adapters 1 CPU1 CXL Logical Devices Domain1 1 Memory DIMM 1 1 CXL Memory Chunk Remote Chunk 1 Ports Endpoints 1 Memory I1 Memory Chunks T1 Ports DIMM1 1 Chunk1 Switches CXL Connections 1 Ports U1 New objects/links D1

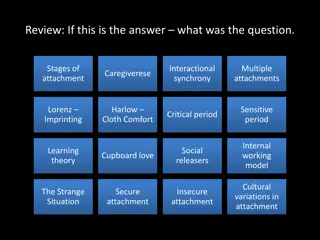

CXL 2.0 memory pooling Single logical device case (color coding denotes binding) Multi logical device case Host1 Host1 Host1 Host2 Host1 Host2 CXL Switch CXL Switch CXL Switch CXL Switch FAM 1 FAM 2 FAM 2 FAM 1

Type 3 SLD Memory Composable Module 2 Chassis PCIe Devices 1 1 1 PCIe Devices Devices PCIe Chassis2 PCIe PCIe Functions Functions CXL Logical Devices Memory Domains 1 Fabric Adapters 1 1 1 Memory Memory Chunks DIMM1 Ports 1 1

Type 3 MLD Memory Chassis Chassis2 PCIe Devices Devices Devices 1 PCIe PCIe Memory Domains Fabric Adapters 1 1 PCIe Functions 2 1 CXL Logical Devices 2 1 Memory Chunks Ports Memory 2 1 1 DIMM1