Development of Techniques and Tools for Chip Interconnection at INFN and UK Groups

Proposals received from INFN (Bari and Trieste) focus on developing techniques for bending wafer-scale chips and studying the impact of curvature on performance. UK Groups like Brunel University and University of Liverpool are involved in sensor design and testing. Additionally, US group BNL is working on the 65nm TJ process and contributing to sensor development for various projects.

Download Presentation

Please find below an Image/Link to download the presentation.

The content on the website is provided AS IS for your information and personal use only. It may not be sold, licensed, or shared on other websites without obtaining consent from the author.If you encounter any issues during the download, it is possible that the publisher has removed the file from their server.

You are allowed to download the files provided on this website for personal or commercial use, subject to the condition that they are used lawfully. All files are the property of their respective owners.

The content on the website is provided AS IS for your information and personal use only. It may not be sold, licensed, or shared on other websites without obtaining consent from the author.

E N D

Presentation Transcript

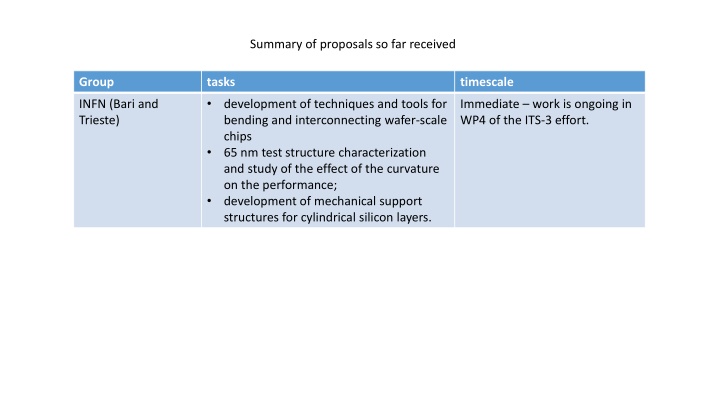

Summary of proposals so far received Group tasks timescale INFN (Bari and Trieste) development of techniques and tools for bending and interconnecting wafer-scale chips 65 nm test structure characterization and study of the effect of the curvature on the performance; development of mechanical support structures for cylindrical silicon layers. Immediate work is ongoing in WP4 of the ITS-3 effort.

Group tasks timescale UK Groups: Brunel University Daresbury Laboratory RAL CMOS Sensor Design Group (CSDG) RAL Particle Physics Division (PPD) University of Birmingham University of Glasgow University of Lancaster University of Liverpool University of York 2021 2022 2023 The timeline to the left is taken from the draft WP and tasks circulated to the eic-rd- silicon mailing list on 10 May 2020. Testing and characterization of MLR1 Sensor design for MLR2 or ER MLR2 submission Testing and characterization of MLR2 Sensor design for ER ER submission Silicon design work is in progress and has been ongoing as part of ERD-25 effort. Testing and characterization of ITS3 ER and assessment of yield Assessment and planning for EIC sensor fork of ITS3 design Fork off sensor design and work on EIC variant for staves and discs (may move to next year depending on results) ER submission for EIC variant sensor for staves and discs (may move to next year depending on results) 2024 Testing and characterization of EIC ER and assessment of yield Si design for EIC ER2 ER2 submission for EIC variant sensor for staves and discs Level of effort going forward will depend on funding. + physics performance simulations all along

Group tasks timescale US group BNL (Instrumentation Division) 2021 Design work on the 65 nm TJ process should commence as soon as the NDA and PDK are delivered. Level of efforts will be dependent upon available generic R&D, project R&D and ultimately project funding TJ65nm NDA setting up in place, acquisition of TJ65nm PDK, obtaining process information for device level analyses and simulations, Define specification of SEE test vehicle ASIC (SEETJ65), start of the design, 2022 Completion of the SEETJ65 design and submission for ER, Building test setup and perform SEE (SEU, SET, SET) cross-section measurements Development of blocks for common ITS3 design Contribution to sensor design for ITS3 ER 2023 Testing and characterization of ITS3 ER and assessment of yield Assessment and planning for EIC sensor fork of ITS3 design Contribution to EIC variant sensor for staves and discs for ER submission Contribution to adaptation of ITS3 design for use in EIC inner layers Contribution to prototyping: stave/disc integration and construction, thermomechanical simulations and detector infrastructure Development of Electronics Readout Laboratory, Beam and Radiation tests

Group tasks timescale US group BNL (Instrumentation Division) 2024 Testing and characterization of EIC ER and assessment of yield Contribution to Si design for EIC ER2 Contribution to EIC variant sensor for staves and discs for ER2 submission Contribution to adaptation of ITS3 design for use in EIC inner layers and integration of design into ER2 if necessary Contribution to prototyping: stave/disc integration and construction, thermomechanical simulations and detector infrastructure Development of Electronics Readout Laboratory, Beam and Radiation tests 2025 Repeat tasks from FY24 as needed