Development Status and Next Steps in Firmware and Software Integration

Firmware and software development updates for FPGA control, real-time data path testing, and readout processes. Progress made in testing and verification of various interfaces. Next steps include completing real-time path tests with multiple FPGAs and bug fixes in IPBus mapping. The software side involves documentation, integration, and testing in various modules and tools. Recent improvements in the forward region integration. Future plans include commissioning with ROD interface and integration with TREX, LATOME, and L1Topo. Detailed status summaries and action items for continued progress.

Download Presentation

Please find below an Image/Link to download the presentation.

The content on the website is provided AS IS for your information and personal use only. It may not be sold, licensed, or shared on other websites without obtaining consent from the author.If you encounter any issues during the download, it is possible that the publisher has removed the file from their server.

You are allowed to download the files provided on this website for personal or commercial use, subject to the condition that they are used lawfully. All files are the property of their respective owners.

The content on the website is provided AS IS for your information and personal use only. It may not be sold, licensed, or shared on other websites without obtaining consent from the author.

E N D

Presentation Transcript

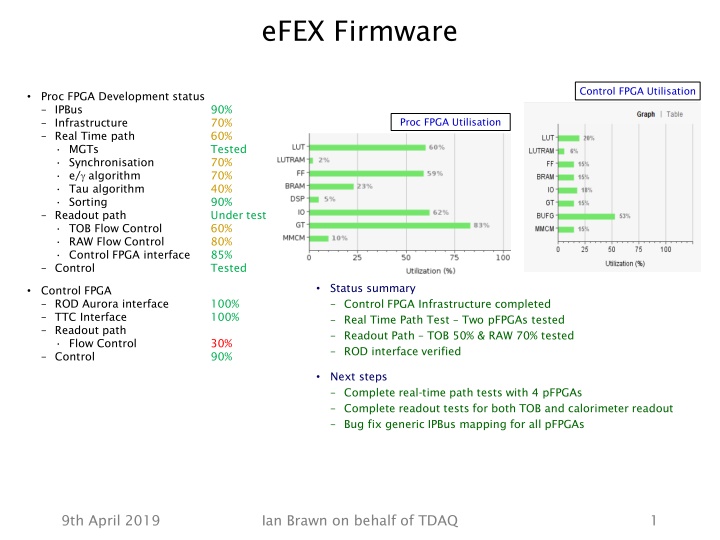

eFEX Firmware Control FPGA Utilisation Proc FPGA Development status IPBus Infrastructure Real Time path MGTs Synchronisation e/ algorithm Tau algorithm Sorting Readout path TOB Flow Control RAW Flow Control Control FPGA interface Control 90% 70% 60% Tested 70% 70% 40% 90% Under test 60% 80% 85% Tested Proc FPGA Utilisation Status summary Control FPGA Infrastructure completed Real Time Path Test Two pFPGAs tested Readout Path TOB 50% & RAW 70% tested ROD interface verified Control FPGA ROD Aurora interface TTC Interface Readout path Flow Control Control 100% 100% 30% 90% Next steps Complete real-time path tests with 4 pFPGAs Complete readout tests for both TOB and calorimeter readout Bug fix generic IPBus mapping for all pFPGAs 9th April 2019 Ian Brawn on behalf of TDAQ 1

eFEX Software, Documentation & Integration Software Register map (XML) Module Control Package Calibration Database Tools Connectivity Database Tools SW-ROD Plugin Diagnostics Tools Monitoring Histograms Test Vector Generation Bit-wise simulation Integration LATOME/LAr TREX/Tile L1Topo DCS Hub/ROD TTC Hub/ROD readout FELIX SwROD TDAQ xx% xx% xx% xx% xx% xx% xx% xx% xx% xx% xx% xx% xx% xx% xx% xx% xx% xx% Documentation User Manual Data Formats Algorithm Specification xx% xx% xx% xx% Status Summary Next Steps 9th April 2019 Ian Brawn on behalf of TDAQ 2

jFEX Firmware Proc FPGA Development status Real-time data path MGTs Jet, ET/MET, Pileup algorithm Large-R Jet, Tau algorithm Readout path Data Merging Packet creation Register definitions ROD interface Control 100% / Under Test 100% 70% (1st version implemented) 90% 80% 80% 60% Under test Control FPGA Ethernet / IPbus Board Monitoring Under test Under test Status summary / Recent news Significant improvement on the forward region Integration is well-advanced Next steps Commission w/ ROD interface Commission w/ TREX, LATOME, L1Topo 9th April 2019 Ian Brawn on behalf of TDAQ 3

jFEX Software, Documentation & Integration Software Register map (XML) Module Control Package Calibration Database Tools Connectivity Database Tools SW-ROD Plugin Diagnostics Tools Monitoring Histograms Test Vector Generation Bit-wise simulation Integration LATOME/LAr TREX/Tile L1Topo DCS Hub/ROD TTC Hub/ROD readout FELIX SwROD TDAQ xx% xx% xx% xx% xx% xx% xx% xx% xx% xx% xx% xx% xx% xx% xx% xx% xx% xx% Documentation User Manual Data Formats Algorithm Specification xx% xx% xx% xx% Status Summary Next Steps 9th April 2019 Ian Brawn on behalf of TDAQ 4

gFEX Firmware Proc FPGA Real time path LAr/Tile Inputs Synchronisation Large-R jets algorithm Under test Global algorithms Readout path Flow Control Control FPGA interface Under test Control Development status Under test Under test Under test Proc FPGA Utilisation Under test Under test N/A Under test Latency Measurement: 280 MHz clock Control FPGA Real time path Synchronisation Readout path Flow Control FELIX interface Control Time label and description Time (clks) Time (ns) 60% Under test T0 output of skew compensation block 0 0 60% Under test 50% T1 output of gTower builder (calibr. gTowers) 19 67.9 T2 partial sum for neighbor calculated 31 110.7 Status summary Testing taking place with gFEX FELIX setup at BNL using dummy input data loaded into playback memories T3 partial sum TX output 36 128.6 T4 partial sum RX input 40 142.9 Next step(s) Test algorithms on 107 events with simplified timing Incorporate realistic flow control into readout Incorporate forward region (| | > 2.4) Test readout with algorithmic (MC) data T5 partial sum input to jet engine 44 157.1 5 T6 Large R jet sum output 46 164.3 T7 TOB_1 ready signal 61 217.9 9th April 2019 Ian Brawn on behalf of TDAQ

gFEX Software, Documentation & Integration Software Register map (XML) Module Control Package Calibration Database Tools Connectivity Database Tools SW-ROD Plugin Diagnostics Tools Monitoring Histograms Test Vector Generation Bit-wise simulation Integration LATOME/LAr TREX/Tile L1Topo DCS FELIX TTC FELIX readout SwROD TDAQ xx% xx% xx% xx% xx% xx% xx% xx% xx% xx% xx% xx% xx% xx% xx% xx% xx% Documentation User Manual Data Formats Algorithm Specification xx% xx% xx% xx% Status Summary Next Steps 9th April 2019 Ian Brawn on behalf of TDAQ 6

L1Topo Firmware Proc FPGA Development status Realtime data path MGTs Decoding of input TOBs Baseline Algorithms Readout path Data Merging Packet creation Register definitions ROD interface Control 90% 100% / Under Test 75% 100% Resource utilization: Multiplicity Topo Use Topo1b, assume all 110 output bits are jets 40 2 bit and 10 3 bit jet multiplicities Numbers of input jets: 64 Jets, 128 Jets and 256 Jets 80% 60% 70% 40% Under test Control FPGA Ethernet / IPbus Board Monitoring Under test Under test Topo LUT utilisation for different jet implementations Status summary Integration well advanced Submission deadline for new algorithms: 30.6.19 Next steps Finalizing decoding of input TOBs Commissioning of interfaces 9th April 2019 Ian Brawn on behalf of TDAQ 7

L1Topo Software, Documentation & Integration Software Register map (XML) Module Control Package Calibration Database Tools Connectivity Database Tools SW-ROD Plugin Diagnostics Tools Monitoring Histograms Test Vector Generation Bit-wise simulation Integration eFEX jFEX gFEX CTP DCS Hub/ROD TTC Hub/ROD readout FELIX SwROD TDAQ xx% xx% xx% xx% xx% xx% xx% xx% xx% xx% xx% xx% xx% xx% xx% xx% xx% xx% xx% Documentation User Manual Data Formats Algorithm Specification xx% xx% xx% xx% Status Summary Next Steps 9th April 2019 Ian Brawn on behalf of TDAQ 8

Hub Firmware Design Area 1 Item 1 Item 2 Utilisation chart from Vivado, etc. Design Area 3 Item 1 Item 2 Status summary / Recent news Next steps 9th April 2019 Ian Brawn on behalf of TDAQ 9

Hub Software, Documentation & Integration Software Register map (XML) Module Control Package Calibration Database Tools Connectivity Database Tools SW-ROD Plugin Diagnostics Tools Monitoring Histograms Test Vector Generation Bit-wise simulation Integration ROD eFEX jFEX L1Topo DCS TTC FELIX SwROD TDAQ xx% xx% xx% xx% xx% xx% xx% xx% xx% xx% xx% xx% xx% xx% xx% xx% xx% xx% Documentation User Manual Data Formats Algorithm Specification xx% xx% xx% xx% Status Summary Next Steps 9th April 2019 Ian Brawn on behalf of TDAQ 10

ROD Firmware Backplane Interface Development status eFEX interface Aurora (3 channels) All channels Readout/CTTC Status Registers jFEX interface Aurora Bus width adapter All channels Status Registers Testing in jfex shelf Topo interface 80% Tested 70% 80% 60% eFEX-ROD FPGA Utilisation 80% 80% 50% 60% 10% not started Packet Processor TOB/xTOB packets Event building All header/trailer fields Control/Status registers Debug Queue Bulk Data Handling Specification Design 80% 70% 70% 10% jFEX-ROD FPGA Utilisation 80% 50% Status summary / Recent news [optional] 1st HW test with eFEX packets complete Next step(s) PRR, Bulk Data implementation, Debug Queue 3rd June 2019 Ian Brawn on behalf of TDAQ 11

ROD Software, Documentation & Integration Software Register map (XML) Module Control Package Calibration Database Tools Connectivity Database Tools SW-ROD Plugin Diagnostics Tools Monitoring Histograms Test Vector Generation Bit-wise simulation Integration Hub eFEX jFEX L1Topo DCS TTC FELIX SwROD TDAQ xx% xx% xx% xx% xx% xx% xx% xx% xx% xx% xx% xx% xx% xx% xx% xx% xx% xx% Documentation User Manual Data Formats Algorithm Specification xx% xx% xx% xx% Status Summary Next Steps 9th April 2019 Ian Brawn on behalf of TDAQ 12

TREX Firmware (1) PREDATOR FPGA (Kintex UltraScale) Development status Real-time path LVDS data reception Autom. input delay scan De-BCMUX-ing Data formatting Transmission to FEXes Readout path G-Link formatting Transmission to legacy ROD Transmission to FELIX Configuration, Control & Monitoring System monitoring (SYSMON) Interface to VME (via PPM/ExtReM) Interface to FireFly transc. (I2C master) Tested Interface to Zynq+ MPSoc (I2C slave) FPGA & MPSoC Utilisation (master/official releases only) Tested 10% Tested 40% 40% 80% 30% 30% Tested Tested 20% DINO FPGAs (4x Artix-7) Real-time path LVDS duplication Transmission to CP & JEP Routing to PREDATOR FPGA Monitoring System monitoring (XADC) Interface to VME/Zynq+ (I2C slave) Tested Tested Tested Tested To be tested 9th April 2019 Ian Brawn on behalf of TDAQ 13

TREX Firmware (2) ExtReM FPGA (Virtex-1000E, on PPM) Development status Readout path Remove G-Link formatting Route TTC signals to PREDATOR Tested Configuration & Control (from VME) Interface to PREDATOR Interface to Zynq+ Register model for PREDATOR Register model for Zynq+ I2C master interface to TREX FPGA & MPSoC Utilisation (master/official releases only) Tested Tested To be tested Tested 80% 90% Zynq+ MPSoC (from TREX pre-production only) Configuration, Control & Monitoring (PL) Interface to VME (via PPM/ExtReM) Interface to PS I2C master interf. (slow-control) 30% System monitoring (SYSMON) Slow-ctrl data storage & analysis 30% Slow-control Monitoring (PS) JTAG master OPC/UA server Communication w/ DCS (Ethernet) started 70% Status summary Zynq+ MpSoC to be implemented on the TREX pre- production module (TREX v2; June19) Currently, main focus on finalising the implementation of the real-time interface to FEXes and of the readout interface to the legacy ROD Not started 30% Next step(s) Test legacy real-time path to CP & JEP (CERN bat- 104) Test legacy readout interface to legacy ROD (CERN bat-104) Test real-time interface to FEXes (CERN STF) Not started Not started Not 9th April 2019 Ian Brawn on behalf of TDAQ 14

TREX Software, Documentation & Integration Software Register map Module Control Package Calibration Database Tools Connectivity Database Tools SW-ROD Plugin Diagnostics Tools Monitoring Histograms Test Vector Generation Bit-wise simulation Integration PPM eFEX jFEX gFEX DCS TTC Legacy ROD FELIX SwROD TDAQ xx% xx% xx% xx% xx% xx% xx% xx% xx% xx% xx% xx% xx% xx% xx% xx% xx% xx% xx% Documentation User Manual Data Formats Algorithm Specification xx% xx% xx% xx% Status Summary Next Steps 9th April 2019 Ian Brawn on behalf of TDAQ 15

STF Slice Tests Not Done/ In progress / Done Not Done/ In progress / Done Not Done/ In progress / Done Not Done/ In progress / Done Not Done/ In progress / Done Not Done/ In progress / Done Not Done/ In progress / Done Not Done/ In progress / Done Not Done/ In progress / Done Not Done/ In progress / Done Not Done/ In progress / Done Not Done/ In progress / Done Not Done/ In progress / Done Not Done/ In progress / Done Not Done/ In progress / Done Not Done/ In progress / Done Not Done/ In progress / Done Not Done/ In progress / Done Not Done/ In progress / Done Not Done/ In progress / Done Not Done/ In progress / Done Not Done/ In progress / Done Not Done/ In progress / Done Not Done/ In progress / Done Not Done/ In progress / Done Not Done/ In progress / Done Not Done/ In progress / Done Not Done/ In progress / Done Not Done/ In progress / Done Not Done/ In progress / Done TREX eFEX protocol test TREX gFEX protocol test TREX jFEX protocol test eFEX Topo protocol test gFEX Topo protocol test jFEX Topo protocol test eFEX Readout RT data ROD gFEX Readout RT data FELIX jFEX Readout RT data ROD Topo Readout RT data ROD TREX Readout RT data FELIX eFEX data FELIX jFEX/Topo data FELIX FELIX SW ROD Data extraction from SW ROD Full eFEX readout path Full jFEX readout path Full Topo readout path Full gFEX readout path Full TREX readout path eFEX Topo Readout test gFEX Topo Readout test jFEX Topo Readout test TREX eFEX Readout test TREX gFEX Readout test TREX jFEX Readout test TREX eFEX Topo Slice TREX gFEX Topo Slice TREX jFEX Topo Slice Full Slice test 9th April 2019 Ian Brawn on behalf of TDAQ 16