Exploring IRDS Emerging Research Devices and Architectures Workshop

Discover insights from the IRDS Emerging Research Devices and Architectures Workshop, featuring discussions on nanocrossbars, international semiconductor roadmaps, data-centric computing, and more. Join experts like Paul Franzon, An Chen, and Erik DeBenidictis in exploring cutting-edge technologies and innovative approaches shaping the future of the industry.

Download Presentation

Please find below an Image/Link to download the presentation.

The content on the website is provided AS IS for your information and personal use only. It may not be sold, licensed, or shared on other websites without obtaining consent from the author. If you encounter any issues during the download, it is possible that the publisher has removed the file from their server.

You are allowed to download the files provided on this website for personal or commercial use, subject to the condition that they are used lawfully. All files are the property of their respective owners.

The content on the website is provided AS IS for your information and personal use only. It may not be sold, licensed, or shared on other websites without obtaining consent from the author.

E N D

Presentation Transcript

IRDS Emerging Research Devices and Architectures NanoCrossbar Workshop Paul Franzon North Carolina State University Raleigh, NC paulf@ncsu.edu 919.515.7351 http://www.ece.ncsu.edu/erl/faculty/paulf.html

Thanks Thanks to Rambus for hosting this event Spherically Gary Edge, VP for Research and Jaimie Stuart for Logistics 2

Background International Roadmap for Semiconductors (ITRS) used to sponsored by SIA Now International Roadmap for Devices and Systems (IRDS) sponsored by IEEE Emerging Research Devices (ERD) Chapter had a subsection called Emerging Research Architectures (ERA). Both Edited chapter in odd years Help workshops in even years Held a workshop on Storage Class Memory in 2012 Been wanting to do workshops in other areas but lacked good definition For 2016 two workshops Nanocrossbar Approximate/ Stochastic/ Probabilistic computing 3

Core Group - ERA Paul Franzon, NCSU (editor) An Chen, IBM (ERA chair) Shamik Das, Mitre Matthew Marinella, Sandia Erik DeBenidictis, Sandia Geoff Burr , IBM 4

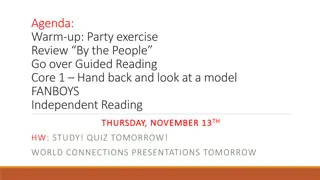

Data-Centric Program-Centric (performance and components dictated by designer) (performance and/or components influenced by the data that is passed through the system) Good old-fashioned Von Neumann Memory Non-Von Neumann Processor Non-VN Processor (including less-than-reliableVN) Trained off-line Trained in-line CMOS Non-CMOS CMOS Non-CMOS CMOS Non-CMOS Active Interconnect CMOS Non-CMOS CMOS Non-CMOS Analog computing (w/ Flash) Execution of pre-trained ANN FPGA SRAM CMOS Coarse-Grained Reconfigurable Architectures New learning algorithms (unsupervised, reinforcement) HTM Crossbars for STDP True North Ohmic Weave DRAM Next switch Deterministic/reliable Coupled oscillators Flash Automata Processing Analog GPUs computing ML NV Accelerators (multimedia, etc.) TCAM NVM- based FPGA Acceler- ators (Convolution, SVM, ML) computing Supervised ANN learning NVM crossbars for S-SCM, M-SCM Logic-in- memory Crossbars for backprop Probabilistic computing Probabilistic Learning deterministic CMOS beyond the design envelope Quantum computing Non- Bayesian Approximate RBM ITRS Winter Meeting, Atlanta, GA, February 10-12, 2016 computing

2015 Chapter Started tracking NanoCrossbars explicitly 6

Goals of Workshop Identify and quantify the state of the art in devices, design, modeling, fabrication, and employment of Nano-enabled Crossbars for computing. Identify the research barriers impeding the use of NanoCrossbars for computing. 7

Questions asked to presenters General, including memories What is the status of achieving linear repeatable response, low power, sufficiently long retention, fast writes, sufficiently distinguishable resistances in different states, and long write endurance in one nanoscale device? Is the access device issue solved? What are the remaining issues? 8

Questions Neuromorphic computing What are the requirements on device linearity, scalability and dynamic range? What is achieved today? What are the tradeoffs exposed in achieving this? What style of non-traditional computing is best suited to nanodevice arrays? E.g. spiking neuron, deep network, full logic map, etc. Why? What are the specific gaps in device properties that are preventing us from achieving this paradigm? 9

Questions Analog computing What are the requirements on device linearity, scalability and dynamic range? What is achieved today? What are the tradeoffs exposed in achieving this? What is the required device yield? What mechanisms are available for implementing working arrays in the presence of <100% yield? What levels of noise during readout can be tolerated? To what degree could closed-loop control (e.g., iterative resistance-tuning for higher accuracy) be available during device write? 10

Agenda 0900 0930 : Introduction: Paul Franzon, NC State University 0930 1020 : Matt Marinella, Sandia 1020 1040 : Break 1040 : 1120 : Geoff Burr IBM 1120 1200 : Catchup 1200 1300 : Lunch 1340 : Dmitri Strukov, UCSB 1420 : Kevin Cao, ASU 1420 1440 : Break 1440 - 1520: Miao Hu, HPE 520 1600 : Wei Lu, UMich 1600 1640 : Gert Cauwenberghs, UCSD (via webex) 11