GPMC Configurations for Different Clock Frequencies

Explore GPMC configurations for varying clock frequencies such as 25MHz, 50MHz, and 100MHz. Understand the parameters and setups for optimal performance in burst modes. Images and detailed descriptions provided.

Download Presentation

Please find below an Image/Link to download the presentation.

The content on the website is provided AS IS for your information and personal use only. It may not be sold, licensed, or shared on other websites without obtaining consent from the author. If you encounter any issues during the download, it is possible that the publisher has removed the file from their server.

You are allowed to download the files provided on this website for personal or commercial use, subject to the condition that they are used lawfully. All files are the property of their respective owners.

The content on the website is provided AS IS for your information and personal use only. It may not be sold, licensed, or shared on other websites without obtaining consent from the author.

E N D

Presentation Transcript

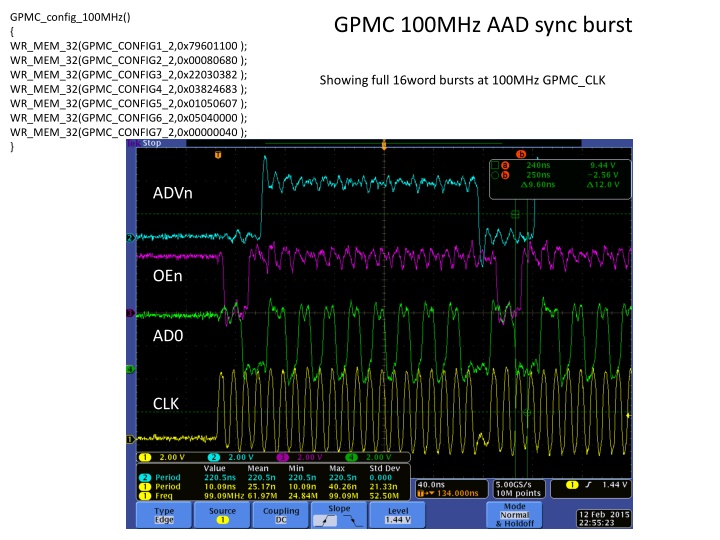

GPMC_config_100MHz() { WR_MEM_32(GPMC_CONFIG1_2,0x79601100 ); WR_MEM_32(GPMC_CONFIG2_2,0x00080680 ); WR_MEM_32(GPMC_CONFIG3_2,0x22030382 ); WR_MEM_32(GPMC_CONFIG4_2,0x03824683 ); WR_MEM_32(GPMC_CONFIG5_2,0x01050607 ); WR_MEM_32(GPMC_CONFIG6_2,0x05040000 ); WR_MEM_32(GPMC_CONFIG7_2,0x00000040 ); } GPMC 100MHz AAD sync burst Showing full 16word bursts at 100MHz GPMC_CLK ADVn OEn AD0 CLK

GPMC 100MHz AAD sync burst Focusing in on address phase and beginning of data bursts. OEn signifies first address, WEn (on next slide) is second address phase. 1st 2nd addr 1st data 2nd burst 3rd burst addr GPMC_CLK = 100MHz ADVn OEn AD0 CLK

GPMC 100MHz AAD sync burst Showing WEn for second address phase. Note 1st data transitions on rising edge, and all subsequent data transitions on falling edge. But all data can be sampled on rising edge. 1st 2nd addr 1st data 2nd burst 3rd burst addr ADVn WEn AD0 CLK

GPMC_config_50MHz() { WR_MEM_32(GPMC_CONFIG1_2,0x79601101 ); WR_MEM_32(GPMC_CONFIG2_2,0x00100c80 ); WR_MEM_32(GPMC_CONFIG3_2,0x44060684 ); WR_MEM_32(GPMC_CONFIG4_2,0x06848c86 ); WR_MEM_32(GPMC_CONFIG5_2,0x020a0c0e ); WR_MEM_32(GPMC_CONFIG6_2,0x0a080000 ); WR_MEM_32(GPMC_CONFIG7_2,0x00000040 ); } GPMC 50MHz AAD sync burst Showing full 16word bursts at 50MHz GPMC_CLK. Parameters are doubled, CLKDIV=2 ADVn OEn AD0 CLK

GPMC 50MHz AAD sync burst Focusing in on address phase and beginning of data bursts. OEn signifies first address, WEn (not shown) is second address phase. Data sampled on same edges as in 100MHz mode 1st 2nd addr 1st data 2nd burst 3rd burst addr ADVn OEn AD0 CLK

GPMC_config_25MHz() { WR_MEM_32(GPMC_CONFIG1_2,0x79601113 ); WR_MEM_32(GPMC_CONFIG2_2,0x00100c80 ); WR_MEM_32(GPMC_CONFIG3_2,0x44060684 ); WR_MEM_32(GPMC_CONFIG4_2,0x06848c86 ); WR_MEM_32(GPMC_CONFIG5_2,0x020a0c0e ); WR_MEM_32(GPMC_CONFIG6_2,0x0a080000 ); WR_MEM_32(GPMC_CONFIG7_2,0x00000040 ); } GPMC 25MHz AAD sync burst Showing full 16word bursts at 25MHz GPMC_CLK. Parameters are same as 50MHz, just PARAGRANULARITY bit is set to double all parameters. CLKDIV=4 ADVn OEn AD0 CLK

Focusing in on address phase and beginning of data bursts again. OEn signifies first address, WEn (not shown) is second address phase. Data sampled on same edges as in 100/50MHz mode GPMC 25MHz AAD sync burst 1st 2nd addr 1st data 2nd burst 3rd burst addr ADVn OEn AD0 CLK