IEEE 802.11-19/1921-01-00be Multi-link Architecture Overview

Exploring the multi-link architecture proposal IEEE 802.11-19/1921-01-00be, focusing on packet level aggregation for enhanced throughput, load balancing, and latency performance. The design features shared high MAC and independent low MAC/PHY components, emphasizing a single MAC SAP for efficient traffic distribution and management. Receiver and transmitter side functionalities are detailed, showcasing the system's potential to revolutionize wireless communication standards.

Download Presentation

Please find below an Image/Link to download the presentation.

The content on the website is provided AS IS for your information and personal use only. It may not be sold, licensed, or shared on other websites without obtaining consent from the author. If you encounter any issues during the download, it is possible that the publisher has removed the file from their server.

You are allowed to download the files provided on this website for personal or commercial use, subject to the condition that they are used lawfully. All files are the property of their respective owners.

The content on the website is provided AS IS for your information and personal use only. It may not be sold, licensed, or shared on other websites without obtaining consent from the author.

E N D

Presentation Transcript

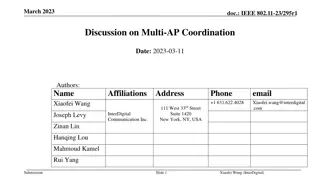

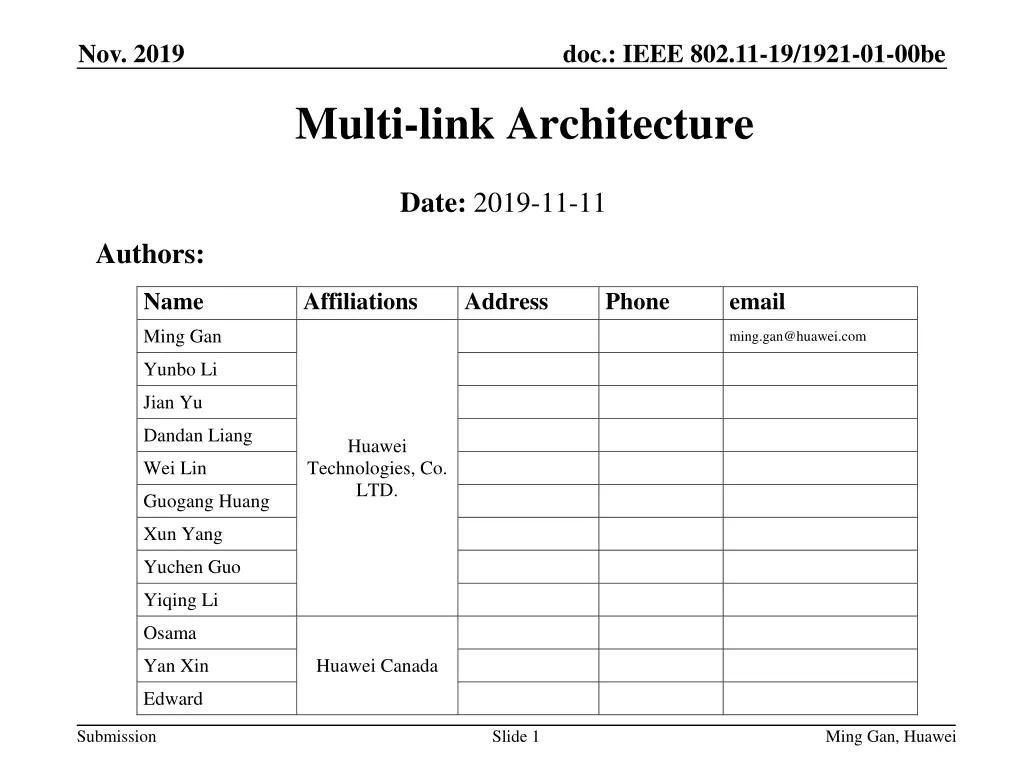

Nov. 2019 doc.: IEEE 802.11-19/1921-01-00be Multi-link Architecture Date: 2019-11-11 Authors: Name Affiliations Address Phone email Ming Gan ming.gan@huawei.com Yunbo Li Jian Yu Dandan Liang Huawei Wei Lin Technologies, Co. LTD. Guogang Huang Xun Yang Yuchen Guo Yiqing Li Osama Yan Xin Huawei Canada Edward Submission Slide 1 Ming Gan, Huawei

Nov. 2019 doc.: IEEE 802.11-19/1921-01-00be Background Two configurations for multi-link were proposed in [1] Packet level aggregation Flow level aggregation Packet level aggregation is much more promising compared with flow level aggregation Increases the peak throughput of a TID by enabling simultaneous operations in different links Dynamic load balance of a TID Improves the robustness and latency performance by duplicate transmission over more than one link and so on In this work, we just show our opinion on the architecture for packet level aggregation (MLD) Try to reuse the existing PHY and MAC Submission Slide 2 Ming Gan, Huawei

Nov. 2019 doc.: IEEE 802.11-19/1921-01-00be Multi-link Device Architecture Single MAC SAP For the multi-link device, it has a shared high MAC and a few independent low MAC and PHY components Exposes a single MAC SAP to the upper layer In the high MAC, perform global sequence number, such association authentication High MAC Common Queues Multilink Management Traffic Steering Low MAC 1 Low MAC 2 At the transmitter side Distribute the traffic to each low MAC, perform load balancing Assign a global sequence number to a received packets from the upper layer Each low MAC is able to perform independent EDCA CCA sounding, may perform security mechanism May maintain the sequence number assignment for link based block acknowledgement as well as link specific MAC processing Buffer Queues Buffer Queues EDCAF EDCAF PHY 1 PHY 2 TX 2 TX 1 Submission Slide 3 Ming Gan, Huawei

Nov. 2019 doc.: IEEE 802.11-19/1921-01-00be Multi-link Device Architecture Single MAC SAP At the receiver side Collect the packets from the multiple links Perform buffer reordering based on the global sequence number, and send them to the upper layer in the order Perform link-based block acknowledgement based on its own scoreboard High MAC Reordering Buffer Multilink Management Common Queues Low MAC 1 Low MAC 2 Global sequence number was assigned for each packet in the high MAC [1] and [2] Is only needed by high MAC layer Can be used for buffer ordering Bigger space size than the sequence number, and needs additional signaling (maybe zero overhead) If using SN field, it can not support legacy fragmentation. RX Buffer RX Buffer Scoreboard Scoreboard PHY 1 PHY 2 RX 2 RX 1 Submission Slide 4 Ming Gan, Huawei

Nov. 2019 doc.: IEEE 802.11-19/1921-01-00be Scoreboard Is that possible to just have one scoreboard shared by more than one STA of the MLD? This kind of scoreboard should be a RAM which provide more than one port to be read and written simultaneously However, true two dual RAM is more expensive than the existing single port RAN Three-port RAM is rarely used now Hence, we suggest to have a scoreboard for each one STA of the MLD. If there is a sequence number for each link, the sizes of each scoreboard could be different, depending on the data rate of the corresponding link There is no overhead for bitmap in BA which could be the same size as today Submission Slide 5 Ming Gan, Huawei

Nov. 2019 doc.: IEEE 802.11-19/1921-01-00be Summary We propose the following items Have a scoreboard for each one STA of the MLD Global sequence number is not indicated by SN field Sequence number for a link could be optionally assigned Submission Slide 6 Ming Gan, Huawei

Nov. 2019 doc.: IEEE 802.11-19/1921-01-00be References [1] IEEE 802.11-19/0823r2 Multi-link aggregation [2] IEEE 802.11-19/1575r0 Multi-link BA operation Submission Slide 7 Ming Gan, Huawei