Improving DRAM Latency with Charge-Level-Aware Techniques

Learn about a novel approach to reducing DRAM latency using charge-level-aware look-ahead partial restoration. This method addresses the significant portion of DRAM access latency caused by cell restoration processes, leading to notable performance gains and energy savings.

Download Presentation

Please find below an Image/Link to download the presentation.

The content on the website is provided AS IS for your information and personal use only. It may not be sold, licensed, or shared on other websites without obtaining consent from the author. If you encounter any issues during the download, it is possible that the publisher has removed the file from their server.

You are allowed to download the files provided on this website for personal or commercial use, subject to the condition that they are used lawfully. All files are the property of their respective owners.

The content on the website is provided AS IS for your information and personal use only. It may not be sold, licensed, or shared on other websites without obtaining consent from the author.

E N D

Presentation Transcript

Reducing DRAM Latency via Charge-Level-Aware Look-Ahead Partial Restoration

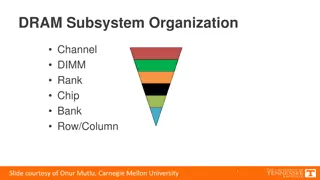

Problem DRAM Cell Restoration latency takes up to 43.6% of DRAM access latency Activation Restoration Refresh Row buffer Page 2 of 6

Motivation Observation: a recently-accessed row is likely to be accessed again soon Page 3 of 6

Our Proposal Page 4 of 6

Results 14.7% performance improvement 11.3% energy reduction Page 5 of 6

Reducing DRAM Latency via Charge-Level-Aware Look-Ahead Partial Restoration Session 3-A, Oct 22