Innovative Financial Services Provider - Extra Value Consulting Pvt. Ltd.

Extra Value Consulting Pvt. Ltd. is a pioneering financial services company catering to the needs of the SME sector since 2007. From business strategy to tax compliance, they offer a wide range of services to help clients thrive. Their experienced team of professionals focuses on delivering value beyond expectations through personalized attention and integrity. Explore their business advisory, tax, regulatory, and accountancy services for insightful solutions tailored to your needs.

Download Presentation

Please find below an Image/Link to download the presentation.

The content on the website is provided AS IS for your information and personal use only. It may not be sold, licensed, or shared on other websites without obtaining consent from the author. If you encounter any issues during the download, it is possible that the publisher has removed the file from their server.

You are allowed to download the files provided on this website for personal or commercial use, subject to the condition that they are used lawfully. All files are the property of their respective owners.

The content on the website is provided AS IS for your information and personal use only. It may not be sold, licensed, or shared on other websites without obtaining consent from the author.

E N D

Presentation Transcript

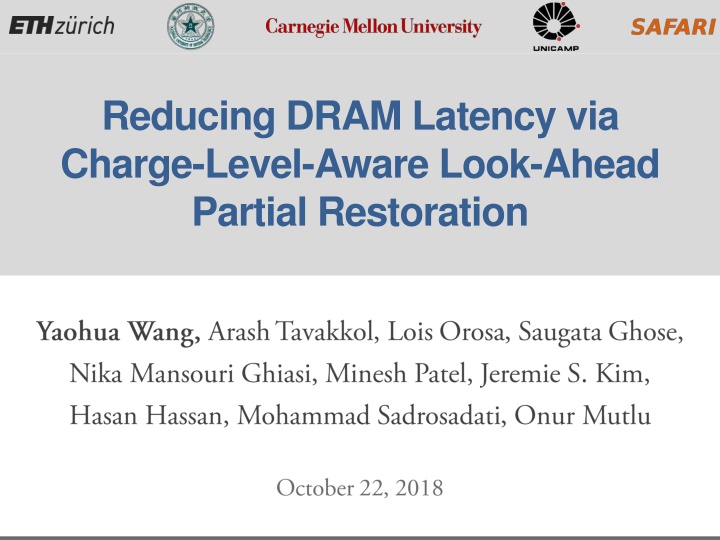

Reducing DRAM Latency via Charge-Level-Aware Look-Ahead Partial Restoration

Executive Summary Page 2 of 22

Outline Background: Accessing Data in DRAM Key Observations on Partial Restoration Charge-Level-Aware Look-Ahead Partial Restoration Evaluation Conclusion Page 3 of 22

Fundamental DRAM Operations Page 4 of 22

Reducing Latency with Partial Restoration Charge Level Charge Level Decay Full Full Min Min 64ms 64ms Ref Ref Ref Acc Acc Ref Acc Acc Page 5 of 22

Outline Background: Accessing Data in DRAM Key Observations on Partial Restoration Charge-Level-Aware Look-Ahead Partial Restoration Evaluation Conclusion Page 6 of 22

More Significant Opportunities for Partial Restoration [0,16] [16,32] [32,48] [48,64] >64 (ms) 100% Interval Distribution 90% 80% 70% 60% 50% mix1 mix2 mix3 mix4 mix5 mix6 mix7 mix8 mix9 mix10 Page 7 of 22

Predicting If a Cell Is Reactivated Soon (in 16ms) (Small, Small) (Small, Large) (Large, Small) (Large, Large) 100% Distribution Interval Pair 75% 50% 25% 0% mix1 mix2 mix3 mix4 mix5 mix6 mix7 mix8 mix9 mix10 Page 8 of 22

Balancing Activation/Restoration Latency Reductions Bitline Voltage activation done Time Page 9 of 22

Minimizing the Total DRAM Access Latency Bitline Voltage activation done Time Page 10 of 22

Summary of Key Observations Page 11 of 22

Outline Background: Accessing Data in DRAM Key Observations on Partial Restoration Charge-Level-Aware Look-Ahead Partial Restoration Evaluation Conclusion Page 12 of 22

Overview of CAL Page 13 of 22

Tracking Access-to-Access Intervals Timer Table Insert [PRE] Tag Timer PR V Initialize [PRE] Counts down Every 1ms Page 14 of 22

Outline Background: Accessing Data in DRAM Key Observations on Partial Restoration Charge-Level-Aware Look-Ahead Partial Restoration Evaluation Conclusion Page 15 of 22

Evaluation Methodology Page 16 of 22

Comparison Points Page 17 of 22

Performance Improvement Over DDR4 Baseline CC RT CCRT CAL IdealCAL Normalized Performance 1.30 Single-Core 8-Core 1.25 1.20 1.15 1.10 1.05 1.00 Memory Non- Intensive Memory Intensive 25% Memory Intensive 50% Memory Intensive 75% Memory Intensive 100% Memory Intensive Page 18 of 22

Energy Savings Over DDR4 Baseline Base CC RT CAL 100% Energy Consumption 80% 60% 40% 20% 0% Memory Non- Intensive Memory Intensive 25% Memory Intensive 50% Memory Intensive 75% Memory Intensive 100% Memory Intensive Single-Core 8-Core Page 19 of 22

Other Results in Our Paper Page 20 of 22

Conclusion Page 21 of 22

Reducing DRAM Latency via Charge-Level-Aware Look-Ahead Partial Restoration

Backup Slides Page 23 of 22

Partial Restoration Page 24 of 22

15ms VS 16ms Page 25 of 22

Per-core Timer Table Design Page 26 of 22

Memory Intensity and Access Interval Page 27 of 22

What If Applications with Large Access Intervals Page 28 of 22

The Uniform Interval Distributions Page 29 of 22

Handling Large Access-to-access intervals Page 30 of 22

Trade-off between tRCD and tRAS reduction Page 31 of 22

3. Area and Power Overhead Page 32 of 22

Timer Table Size Page 33 of 22

Different Restoration Levels Page 34 of 22

Different Refresh Interval Page 35 of 22

Activation and Restoration Latency Reduction Trade-off Page 36 of 22

Key Idea & Structure of CAL Timer Table Tag Timer PR V Page 37 of 22

Exploiting Charge Levels to Reduce Latency Page 38 of 24

Exploiting Charge Levels to Reduce Latency Page 39 of 24