Innovative FPGA Architecture Utilizing Memristor-Based Reconfiguration

Discover the groundbreaking research on mrFPGA, a unique FPGA architecture incorporating memristor technology for reconfiguration. Explore key concepts such as memristor integration, adaptive buffer insertion, and advanced CAD software. Evaluation against benchmarks showcases significant improvements in area, speed, and power efficiency. This study presents a promising step towards more efficient and scalable FPGA designs.

Download Presentation

Please find below an Image/Link to download the presentation.

The content on the website is provided AS IS for your information and personal use only. It may not be sold, licensed, or shared on other websites without obtaining consent from the author. If you encounter any issues during the download, it is possible that the publisher has removed the file from their server.

You are allowed to download the files provided on this website for personal or commercial use, subject to the condition that they are used lawfully. All files are the property of their respective owners.

The content on the website is provided AS IS for your information and personal use only. It may not be sold, licensed, or shared on other websites without obtaining consent from the author.

E N D

Presentation Transcript

MRFPGA: A NOVEL FPGA ARCHITECTURE WITH MEMRISTOR-BASED RECONFIGURATION Data Storage Systems and Networks Lab. October 2011 Ali Ahari

Outline Introduction Ideas Evaluation Conclusion

Introduction We are going to talk about mrFPGA a paper by Jason Cong and Bingjun Xiao from UCLA which has been appeared in NanoArch 2011

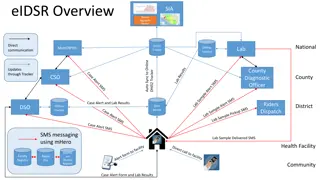

Main Ideas Using memristor in configuration bits No need for 3D-Die stacking Capacitance shielding Adaptive buffer insertion New CAD software

Memresistor in RC Scalable below 30nm Fully compatible with CMOS Programming time 5ns in 180nm Tech.

Evaluation Against Virtex 6 20 MCNC benchmarks 5.18x area savings 2.28x speed-up 1.63x power savings

Conclusion Not a new approach