ISO15693 Analysis

Analysis of a problem where 2 extra dummy bytes were read through the SPI interface from the TRF796x in the context of ISO15693. Includes the root cause, modifications required in SPI.c, and TRF796x.c, along with recommendations for resolving the issue effectively.

Download Presentation

Please find below an Image/Link to download the presentation.

The content on the website is provided AS IS for your information and personal use only. It may not be sold, licensed, or shared on other websites without obtaining consent from the author.If you encounter any issues during the download, it is possible that the publisher has removed the file from their server.

You are allowed to download the files provided on this website for personal or commercial use, subject to the condition that they are used lawfully. All files are the property of their respective owners.

The content on the website is provided AS IS for your information and personal use only. It may not be sold, licensed, or shared on other websites without obtaining consent from the author.

E N D

Presentation Transcript

ISO15693 Analysis Erick Macias TI Confidential - Internal Only

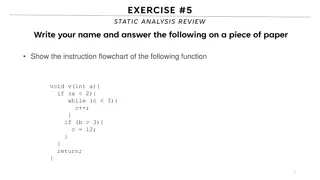

Problem Overview ISO15693 Read Inventory: 2 extra dummy bytes were read through the SPI interface from the TRF796x. The problem was successfully recreated on the TRF7961 EVM as shown in the next slide.

Original ISO15693 Read Inventory Root Cause Extra 2 0 s

Modified ISO15693 Read Inventory Modified SPI.c

Required Changes SPI.c modifications: Remove the reading of extra 2 bytes in SpiReadCont(). Reset the SPI module before modifying the control register Note: When the MCU was not resetting the SPI module it was causing the MOSI line to stay high till the next clock cycle.

Required Changes (cont.) trf796x.c modifications: Read the FIFO status register before reading the FIFO register Note: The TRF796x has a FIFO (12 bytes long), thus when the interrupt would fire with an IRQ status value of 0x60 the TRF796x has received data (9 bytes) into the FIFO, but is not complete yet. However, I would recommend to read the FIFO status register first, to ensure that we read the FIFO based on the FIFO status register.