Performance Estimation Models in IEEE802.15.3e Stack ACK Presentation

Explore the performance estimation models presented by Itaru Maekawa from JRC in the IEEE802.15.3e Stack ACK submission. The presentation covers key concepts, time domain MAC behavior, stack ACK vs. block ACK, and practical implications for HRCP. Analyze bandwidth-saving techniques, complexity trade-offs, and throughput calculations in MAC communication.

Download Presentation

Please find below an Image/Link to download the presentation.

The content on the website is provided AS IS for your information and personal use only. It may not be sold, licensed, or shared on other websites without obtaining consent from the author. If you encounter any issues during the download, it is possible that the publisher has removed the file from their server.

You are allowed to download the files provided on this website for personal or commercial use, subject to the condition that they are used lawfully. All files are the property of their respective owners.

The content on the website is provided AS IS for your information and personal use only. It may not be sold, licensed, or shared on other websites without obtaining consent from the author.

E N D

Presentation Transcript

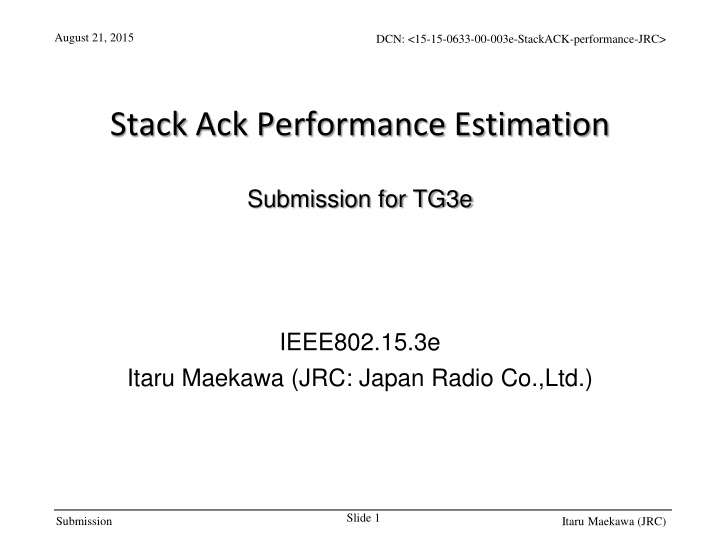

August 21, 2015 DCN: <15-15-0633-00-003e-StackACK-performance-JRC> Stack Ack Performance Estimation Submission for TG3e IEEE802.15.3e Itaru Maekawa (JRC: Japan Radio Co.,Ltd.) Slide 1 Submission Itaru Maekawa (JRC)

August 21, 2015 Simple Stack ACK DCN: <15-15-0633-00-003e-StackACK-performance-JRC> - Key Concept of HRCP MAC - #2 - Block ACK Effective way to save & share bandwidth among multiple devices, especially under high error or collision environments, however .This method has the following disadvantages: Higher complexity Small benefit versus cost (complexity) for use cases of HRCP Larger buffer memory Larger potential latency Stack ACK Stacked Coin FIFO Buffer Practical way for HRCP, because Bandwidth saving is not required, thanks to good BER environment Lower Complexity , simple hardware requirements Slide 2 Submission Itaru Maekawa (JRC)

August 21, 2015 Time Domain MAC Behavior DCN: <15-15-0633-00-003e-StackACK-performance-JRC> Dev.A Dev.B Sub-F#N+4 Sub-F#N+3 Sub-F#N+2 Sub-F#N+1 ACK#M SIFS SIFS Sub-F#M+4 Sub-F#M+3 Sub-F#M+2 Sub-F#M+1 ACK#N+4 Time #1 Data Error Or Buffer full Dev.A Dev.B Sub-F#N+8 Sub-F#N+7 Sub-F#N+6 Sub-F#N+5 ACK#M+4 SIFS Sub-F#M+8 Sub-F#M+7 Sub-F#M+6 Sub-F#M+5 ACK#N+6 Time #2 Header Error Dev.A Dev.B ACK#M+8 Sub-F#N+10 Sub-F#N+9 Sub-F#N+8 Sub-F#N+7 ACK#M+8 SIFS SIFS IIFS SIFS Sub-F#M+10 Sub-F#M+9 ACK#N+6 ACK#N+6 ACK#N+6 RIFS RIFS Time #3 Dev.A Dev.B ACK#M+10 Sub-F#N+12 Sub-F#N+11 Sub-F#N+10 Sub-F#N+9 Sub-F#N+8 Sub-F#N+7 ACK#M+10 SIFS SIFS SIFS ACK#N+12 Time #4 IIFS IIFS IIFS Sync.lost Dev.A Dev.B ACK#M+12 ACK#M+12 ACK#M+12 ACK#M+12 ACK#N+12 Sub-F#M+14 Sub-F#M+13 Sub-F#M+12 Sub-F#M+11 ACK#N+12 RIFS Time #5 Slide3 Submission Itaru Maekawa (JRC)

August 21, 2015 Stack Ack: Performance Estimation Model DCN: <15-15-0633-00-003e-StackACK-performance-JRC> MAC HCS FCS MPDU#N Subheader#N Subframe#N Subframe #N+31 Subframe #N+17 Subframe #N+16 MAC Header PHY Header Subframe #N+15 Subframe #N+1 Subframe #N MAC Header PHY Header HCS HCS SIFS SIFS SIFS Tperiod MAC Header PHY Header MAC Header PHY Header HCS HCS Time Parameters : Example unit 2usec 132bit 0.88Gbps 2.15usec :(BER:bit error rate) PHY Preamble PHY-header+MAC-header +HCS 1760M BPSK, 1/2 ECC. Tpr Lhd Rhead Thd FER=1-(1-BER)Lmpd N - Simplified Estimation Model -When Frame Error is occurred with probability of FER, 50% of Sub-Frames (Average) are retransmitted. 16QAM wo pilot, 14/15 LDPC Rphy Tsifs 6.57Gbps 2usec -MAC Throughput (MACtp) vs FER is calculated as below. mpdu Length Sub-Header+HCS+FCS Aggregation Number Lmpd Lsh N 4kB 11B 16 + / 1 2 1 ( ) FER Lmpd N FER Lmpd N = MACtp Tperiod Tperiod 86.44429usec Tperiod Slide 4 Submission Itaru Maekawa (JRC)

August 21, 2015 Block-Ack :Performance Estimation Model DCN: <15-15-0633-00-003e-StackACK-performance-JRC> MAC HCS FCS MPDU#N Subheader#N Subframe#N Subframe #X MAC Header PHY Header Subframe #N+15 Subframe #N+1 Subframe #N MAC Header PHY Header HCS HCS SIFS SIFS SIFS SIFS Tretry Tperiod MAC Header PHY Header MAC Header PHY Header HCS HCS Time Parameters : Example unit 2usec 132bit 0.88Gbps 2.15usec :(BER:bit error rate) PHY Preamble PHY-header+MAC-header +HCS 1760M BPSK, 1/2 ECC. Tpr Lhd Rhead Thd FER=1-(1-BER)Lmpd N - Simplified Estimation Model -When Frame Error is occurred with probability of FER, ONE Sub-Frames are retransmitted. 16QAM wo pilot, 14/15 LDPC Rphy Tsifs 6.57Gbps 2usec -MAC Throughput (MACtp) vs FER is calculated as below. mpdu Length Sub-Header+HCS+FCS Aggregation Number Lmpd Lsh N 4kB 11B 16 Lmpd + ) N = MACtp + 1 ( Tperiod ( ) Tperiod FER Tretry FER Tperiod Tperiod 86.44429usec Slide 5 Submission Itaru Maekawa (JRC)

August 21, 2015 Stack ACK vs Block-Ack :Throughput Comparison Common Parameters : DCN: <15-15-0633-00-003e-StackACK-performance-JRC> unit 2usec 132bit 0.88Gbps 2usec 11B 4kB PHY Preamble PHY-header+MAC-header +HCS 1760M BPSK, 1/2 ECC. Tpr Lhd Rhead Tsifs Lsh Lmpd Sub-Header+HCS+FCS mpdu Length PHY Rate :6.57Gbps (16QAM, LDPC 14/15 ) Number of Aggregation:16 PHY Rate :52.6Gbps (16QAM x8 MIMO, LDPC 14/15 ) Number of Aggregation:128 FER 4% 100 100 FER 5% Performance Degradation(%) Performance Degradation(%) 99 99 98 98 Stack ACK Stack ACK 97 97 Block ACK Block ACK 96 96 95 1.00E-05 95 1.00E-05 1.00E-11 1.00E-09 1.00E-07 1.00E-11 1.00E-09 1.00E-07 BER BER -Conclusion -As long as FER is less than 10% order, throughput advantage of Block ACK is negligible . -(If FER exceed 10% level, Rate adaptation System should work.) Slide 6 Submission Itaru Maekawa (JRC)