Progress and Testing on SLP1 Design Core by Christos Gentsos at Prisma Paris

"Explore the progress and testing updates on the SLP1 design core by Christos Gentsos at Prisma Paris on 11/3/2015. Learn about the testing methodology, hardware design, and communication protocol development for effective verification."

Download Presentation

Please find below an Image/Link to download the presentation.

The content on the website is provided AS IS for your information and personal use only. It may not be sold, licensed, or shared on other websites without obtaining consent from the author. If you encounter any issues during the download, it is possible that the publisher has removed the file from their server.

You are allowed to download the files provided on this website for personal or commercial use, subject to the condition that they are used lawfully. All files are the property of their respective owners.

The content on the website is provided AS IS for your information and personal use only. It may not be sold, licensed, or shared on other websites without obtaining consent from the author.

E N D

Presentation Transcript

Progress and testing on SLP1 Christos Gentsos, Prisma Paris 11/3/2015

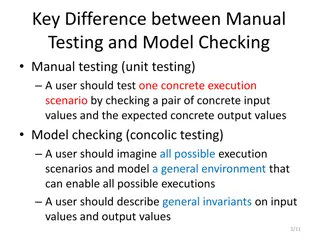

Testing methodology To test the SLP1 design core, a testbench written in SystemVerilog (UVM) was written The testbench, running in Modelsim, creates sample events and verifies the results If we connect the evaluation board with the PC via Ethernet using the IPBus protocol, we can have a simple setup We can call the IPBus communication functions from within the testbench

Testing methodology The hardware necessary to translate IPBus transactions to memory initialization commands (write the AMMap to the board RAM, write the coefficients) and event data transactions is being designed Using Francesco's firmware, I succeeded to communicate with the board via IPBus Some minor hiccups on finding a suitable power supply and power connector for the mezzanine, and on the writing of firmware to communicate with the RAM, but there is progress

Testing methodology In the end we will be able to run testbench code on the actual hardware, which gives us flexibility to possibly write many tests - in a language that is actually meant to do just that Testbench doesn t cover the missing layer functionality yet, but priority is to fully verify the design with all layers and then verify that missing bit