Proposal of LDPC for LPWA in IEEE 802.15.4w

Explore the proposal of LDPC (Low Density Parity Check) for LPWA (Low Power Wide Area) networks in the IEEE P802.15 Working Group. This contribution by Seiji Kobayashi from Sony Semiconductor Solutions aims to enhance forward error correction mechanisms within wireless personal area networks. LDPC offers improved error checking capabilities compared to traditional FEC schemes, as demonstrated in performance comparisons. The document discusses the advantages of LDPC in addressing redundancy concerns and highlights the potential benefits for IEEE 802.15.4w applications. Stay informed about the latest advancements in wireless technology with this insightful submission.

Download Presentation

Please find below an Image/Link to download the presentation.

The content on the website is provided AS IS for your information and personal use only. It may not be sold, licensed, or shared on other websites without obtaining consent from the author. If you encounter any issues during the download, it is possible that the publisher has removed the file from their server.

You are allowed to download the files provided on this website for personal or commercial use, subject to the condition that they are used lawfully. All files are the property of their respective owners.

The content on the website is provided AS IS for your information and personal use only. It may not be sold, licensed, or shared on other websites without obtaining consent from the author.

E N D

Presentation Transcript

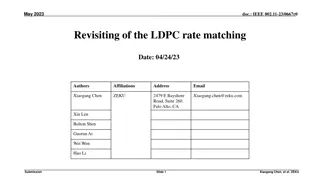

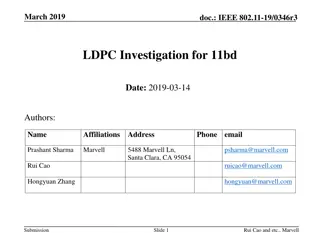

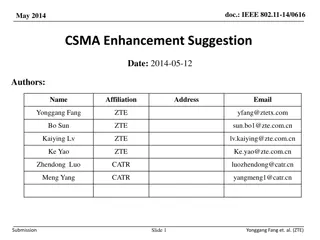

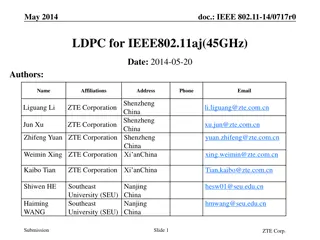

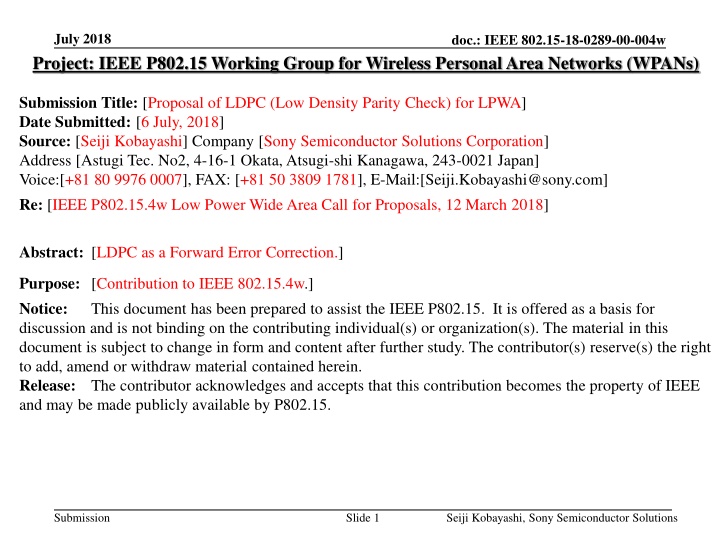

July 2018 Project: IEEE P802.15 Working Group for Wireless Personal Area Networks (WPANs) doc.: IEEE 802.15-18-0289-00-004w Submission Title: [Proposal of LDPC (Low Density Parity Check) for LPWA] Date Submitted: [6 July, 2018] Source: [Seiji Kobayashi] Company [Sony Semiconductor Solutions Corporation] Address [Astugi Tec. No2, 4-16-1 Okata, Atsugi-shi Kanagawa, 243-0021 Japan] Voice:[+81 80 9976 0007], FAX: [+81 50 3809 1781], E-Mail:[Seiji.Kobayashi@sony.com] Re: [IEEE P802.15.4w Low Power Wide Area Call for Proposals, 12 March 2018] Abstract: [LDPC as a Forward Error Correction.] Purpose: [Contribution to IEEE 802.15.4w.] Notice: This document has been prepared to assist the IEEE P802.15. It is offered as a basis for discussion and is not binding on the contributing individual(s) or organization(s). The material in this document is subject to change in form and content after further study. The contributor(s) reserve(s) the right to add, amend or withdraw material contained herein. Release: The contributor acknowledges and accepts that this contribution becomes the property of IEEE and may be made publicly available by P802.15. Submission Slide 1 Seiji Kobayashi, Sony Semiconductor Solutions

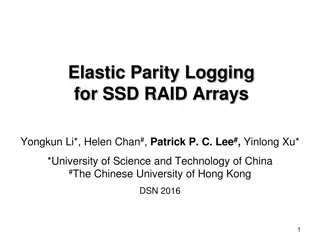

July 2018 doc.: IEEE 802.15-18-0289-00-004w Proposal of LDPC (Low Density Parity Check) for LPWA Seiji Kobayashi (Sony Semiconductor Solutions Corporation), Nabil Loghin (Sony European Technology Center, Stuttgart, Germany) and Ryoji Ikegaya (Sony Semiconductor Solutions Corporation) Submission Slide 2 Seiji Kobayashi, Sony Semiconductor Solutions

July 2018 802.15.4k Forward Error Correction doc.: IEEE 802.15-18-0289-00-004w Current FEC scheme 0 ak + + + + uk uk-1 uk-2 uk-3 uk-4 uk-5 uk-6 1 ak + + + + Rate convolutional coding with constraint length K = 7 has been specified in 802.15.4k. In a practical implementation, additional 6 bits are needed as a purpose of termination , which increases redundancy. 6bits of redundant information is not negligible for a system with small-size payload. LDPC provides error checking function. Submission Slide 3 Seiji Kobayashi, Sony Semiconductor Solutions

July 2018 LDPC (Rate ) performance comparison doc.: IEEE 802.15-18-0289-00-004w Reference: A GPS Synchronized, Long-Range Uplink-Only Radio Designed for IoT, ICC2018 (SAC-IoT 01) 1.2dB In an example shown above, the LDPC (Rate ) outperforms 1.2dB (at BER=10-4 ) against Rate convolutional code with double repetition / spreading. Submission Slide 4 Seiji Kobayashi, Sony Semiconductor Solutions

July 2018 doc.: IEEE 802.15-18-0289-00-004w LDPC Rate (1/4) for 802.15.4w Proposal Parity address table Row and col index 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 1 2 3 4 5 6 7 8 9 10 1 7 90 192 191 71 88 177 242 106 226 133 402 374 378 280 486 489 224 244 482 91 390 506 412 172 197 379 234 111 193 254 165 269 194 209 284 385 255 176 266 285 170 288 256 359 307 396 286 201 368 319 199 316 305 401 174 427 297 283 373 403 321 397 318 420 356 445 312 322 389 496 355 413 380 483 408 480 537 419 475 503 386 444 507 487 425 543 550 499 529 534 410 549 57 22 32 30 86 134 18 129 33 317 53 83 162 166 185 119 26 8 15 43 127 55 164 50 49 70 94 223 84 158 113 354 64 314 259 281 439 156 62 246 72 69 186 81 Submission Slide 5 Seiji Kobayashi, Sony Semiconductor Solutions

July 2018 doc.: IEEE 802.15-18-0289-00-004w LPDC code with rate R=1/4 shall be applied to form Coded Block size of ???????????=4*?????????? where ??????????= SizeMPDU, i.e. 184-bit. Input: 184 bits, denoted as ?0,?1, ,?????? 1with Kldpc = 184 Output: 736 code bits, denoted as ?0,?1, ,?????? 1= ?0,?1, ,?????? 1,?0,?1,?2, ,?????? 1 , with Nldpc = 736 and Mldpc = 552. A systematic binary LDPC code with quasi-cyclic structure (information part) and dual staircase (parity part) shall be used, i.e., parities shall be accumulated (see below). Encoding shall be performed as follows: First: Kldpc = 184 parities shall equal information bits: ??= ??, ??? ? = 0,1, ,????? 1 Initialize: ?0= ?1= ?2= = ?????? 1= 0 Accumulate the first information bit, i0, at parity bit addresses specified in the first row of Table shown in previous page. For example, (all additions are in GF(2)): ?1= ?1?0 ?7= ?7?0 ?90= ?90?0 ?172= ?172?0 ?209= ?209?0 ?359= ?359?0 ?401= ?401?0 ?420= ?420?0 ?483= ?483?0 ?487= ?487?0 For the next 7 information bits, im, m =1, 2, ..., 7, accumulate im at parity bit addresses [x + (m mod 8) Qldpc] mod Mldpc, where x denotes the address of the parity bit accumulator corresponding to the first bit i0, and Qldpc = 69. So for example for information bit i1, the following operations are performed: ?70= ?70?1 ?76= ?76?1 ?159= ?159?1 ?241= ?241?1 ?278= ?278?1 ?428= ?428?1 ?470= ?470?1 ?489= ?489?1 ?0= ?0?1 ?4= ?4?1 For the 9th information bit i8, the addresses of the parity bit accumulators are given in the second row of Table 5-7. In a similar manner the addresses of the parity bit accumulators for the following 7 information bits im, m = 9, 10, ..., 15 are obtained using the formula [ x + (m mod 8) Qldpc] mod Mldpc, where x denotes the address of the parity bit accumulator corresponding to the information bit i8 , i.e. the entries in the second row of Table 5-7. In a similar manner, for every group of 8 new information bits, a new row from the Table 5-7 is used to find the addresses of the parity bit accumulators. After all of the information bits are exhausted, the final parity bits shall be obtained by accumulation as follows: Sequentially perform the following operations starting with i = 1: ??= ???? 1 ??? ? = 1,2, , Mldpc 1 Final content of pi , i = 0, 1,.., Mldpc 1 is equal to the parity bit pi. Submission Slide 6 Seiji Kobayashi, Sony Semiconductor Solutions

July 2018 doc.: IEEE 802.15-18-0289-00-004w Further possibilities Extension of LDPC for longer MSDU sizes. MAC format Fragmentation, Variable length payload, Header FSK modulation method. Pre-amble and Sync for synchronization Submission Slide 7 Seiji Kobayashi, Sony Semiconductor Solutions