SIS20: CMOS ASIC for Solar Irradiance Sensors on Mars Surface

This work presents the development of SIS20, a Mixed-Signal Front-End ASIC designed for Solar Irradiance Sensors to be utilized in the METEO Package of the ExoMars 2020 Mission. The ASIC, developed in collaboration with INTA (National Institute of Aerospace Technologies, Spain), is vital for meteorological stations on the Martian surface, enhancing our understanding of Martian climate and atmospheric dynamics. The ASIC features various processing blocks, control circuitry, and specialized components for accurate solar irradiance measurement in the challenging Martian environment. Explore the detailed ASIC description, experimental results, and conclusions, showcasing the innovation and engineering behind this critical component for Mars exploration.

Download Presentation

Please find below an Image/Link to download the presentation.

The content on the website is provided AS IS for your information and personal use only. It may not be sold, licensed, or shared on other websites without obtaining consent from the author.If you encounter any issues during the download, it is possible that the publisher has removed the file from their server.

You are allowed to download the files provided on this website for personal or commercial use, subject to the condition that they are used lawfully. All files are the property of their respective owners.

The content on the website is provided AS IS for your information and personal use only. It may not be sold, licensed, or shared on other websites without obtaining consent from the author.

E N D

Presentation Transcript

SIS20:A CMOS ASIC for SOLAR IRRADIANCE SENSORS in MARS SURFACE D. V zquez, S. Espejo, J. Ceballos, A. Ragel, C. Aledo, L. Carranza, J.M. Mora, M.A. Lagos

OUTLINE INTRODUCTION ASIC DESCRIPTION EXPERIMENTAL RESULTS CONCLUSIONS

INTRODUCCIN Meteorological instruments typically present in orbital devices, Rovers, probes, etc. Surface instruments complements information provided by orbital devices. In the context of Mars: Meteorological stations in the Surface are critical to understanding the climate and atmospheric dynamics. This work presents SIS20: A Mixed-Signal Front-End ASIC for a Solar Irradiance Sensor to be included in the METEO Package of the ExoMars2020 Mission. It has been conceived in collaboration with INTA (National Institute of Aerospacial Technologies, Spain)

OUTLINE INTRODUCTION ASIC DESCRIPTION EXPERIMENTAL RESULTS CONCLUSIONS

ASIC SIS20: ASIC DESCRIPTION BLOCK DIAGRAM SPI Interface Processing Blocks SRAM Memories and Registers Control circuitry Miscelaneous, etc CLK & POR Instr. Amp & ADC TIA 1 TIA 2 . . . Instr. Amplifier & 16-Bits ADC Trans- Impedance Amplifiers 10-Bits subr. DAC TIA 10 10-Bits DAC (Subranging) Misc. Analog MUXs & Digital BUS Program. Current Sources Global Analog Test Observ. PCS 1 PCS 2 GATOs (References & Test signals) . . . PCS 4 8-Bits Current Steering DAC BANDGAP Vs & Is References Voltage & Current Refs 8-bits CS DAC

ASIC SIS20: ASIC DESCRIPTION BLOCK DIAGRAM SPI Interface Processing Blocks SRAM Memories and Registers Control circuitry Miscelaneous, etc CLK & POR TIA 1 TIA 2 . . . Instr. Amplifier & 16-Bits ADC TIA 10 10-Bits DAC (Subranging) Misc. Analog MUXs & Digital BUS PCS 1 PCS 2 GATOs (References & Test signals) . . . PCS 4 BANDGAP Vs & Is References 8-bits CS DAC

SIS20: ASIC DESCRIPTION RC Networks for Low/High configuration modes TIAs CHANNELS 1M/2pF RC High 100k/20pF RC Low CMOS Switches for Offset meas & compensation Photo-Diode CMOS Switches for gain mode selection Pad 2-stage Folded Cascode OTA Chip 10 channels total: 9 Channels meas 1 Channel calibration. Shared Reference Bias (internal) but external accesing for shielding

SIS20: ASIC DESCRIPTION Dual Slope 50MHz On-chip Clock 16-bit (1-bit sign) ADC Channel and Input Multiplexer COMPARATOR INTEGR. PREAMP-1 PREAMP-2 Data Out Differential Input FSM Level-shift gain EoC Start DIGITAL CONTROL PREAMP-1: Capacitive input impedance Programmable gain 1/50 PREAMP-2: Unity gain Signal accomodation by level shifting TIAs PT1000 VREFs CMOS MUX ADC Internal Signals etc. Preamps can also be used as General purpose VGA.

SIS20: ASIC DESCRIPTION PCS Channels for Temperature Measurement Based on Resistance dependence of PT1000 with temperature CHIP 4-bit resolution Programmable Current Source [0, 750 A] I to V conversion by a digitally controlled 4-bit resolution Current Source From Digital Control To ADC 4 Channels (PT1000) 1 2 3 4 Internal Vref (0.3V) Common Node Ground (0V)

SIS20: ASIC DESCRIPTION 10-bits Sub-ranging DAC Topology based on a conventional resistive ladder structure + multiplexer Used to improve the resolution of the processed data Generates a 10-bit resolution voltaje reference [0; 2,5V] to be connected to the negative rail of the ADC channel. LSB -> 2,441mV

SIS20: ASIC DESCRIPTION 8-bits Current Steering Output DAC 10-bits Subranging DAC Topology based on a conventional resistive ladder structure + multiplexer Off-chip led CS DAC DAC output Used to improve the resolution of the processed data Used for calibration and monitoring Range [0; 25.5mA] LSB -> 100uA Voltage & Current References Generates a 10-bit resolution voltaje reference [0; 2,5V] to be connected to the negative rail of the ADC channel. LSB -> 2,441mV VREF = 2.5V IREF= 100uA BANDGAP OPAMP Feedback Loop External Low Temp Coeff Resistor R ASIC Temperature (PTAT + Res.) & Power Supply (VDD divider) Indicators All Voltage & Current References are derived from VREF & IREF

ASIC SIS DIGITAL BLOCK SPI Communication Interface SPI RSTN SPI SYNC Counter CSN SCLK SDI SDO Data IO Block CONTROL UNIT CTRL BUS DATA & SRAM CONTROLLER & REGISTERS SRAM Generator PULSE COMMAND REGISTER CONTROLLER DATA REG Data Register Memories & Registers STATUS REGISTER CLK/ CONTROL / MONITORING BUS ADDR REG Address Register SAMPLES REGISTER RD REG CTRL Register ACCUMULATOR REGISTERS WR PULSE Pulse Generator SIGMA REGISTER SRAM BUS Processing & Control ERROR PULSE Pulse Generator TEST REGISTER BANK ANALOG CONFIGURATION REGISTERS TO COMPUTING UNIT ANALOG CORE CONTROL UNIT Miscellaneous (Test) BLOCK TEST MUX TEST SIGNALS MUX MUX BARREL SHIFTER GDTO FAST SUM/SUB Clock generator TO ADC MUX DEMUX EOM MATH CLK (50 Mhz) PROCESSOR

OUTLINE INTRODUCTION ASIC DESCRIPTION EXPERIMENTAL RESULTS CONCLUSIONS

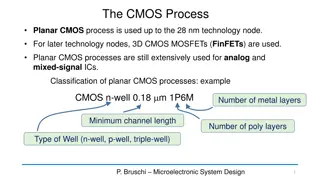

Experimental Results mm 3.3V CMOS 0.35u RHBD (IMSE-RHBDLib) 68 pins mm (I/O pins -> 5.0V) Operating conditions: -125 C to 50 C

Experimental Results TIA Channel in Low & High Gain Modes After leakage current compensation The Slope represents the measured resistance Maximun opamps offset measured over 10 samples: 470 V (@ -125 C)

Experimental Results 16-bits ADC Chain Values accumulated over 256 measurements Good behavior in terms of linearity and noise, but gain and offset errors need to be compensated by calculation @ Earth.

Experimental Results Programmable Voltage Reference [0; 2.5V] through the 10-bit DAC [0;25.5mA] DAC Current @ -125 C 30 25 Output Current [mA] 10-bit Current Steering DAC 20 15 10 5 0 0 10 20 30 40 50 60 Control Word Global Voltage Reference from Bandgap behavior vs Temperature Max. Variation = 21ppm/ C Mean = 2.48V Standard Dev.= 0.45%

OUTLINE INTRODUCTION ASIC DESCRIPTION EXPERIMENTAL RESULTS CONCLUSIONS

Conclusions A Mixed-Signal ASIC (SIS20) in a standard CMOS 0.35mm technology has been presented. It is a Front-End for a Solar Irradiance Sensor on the surface of Mars. (METEO package in the ExoMars2020 mission). RHBD techniques have been applied and use the Rad-Hard Library developed at the Institute of Microelectronics of Seville (IMSE). The ASIC and main block s functionality have been briefly described. The functional operation and technical specifications have been verified in the lab for the specified range of temperature (-125 C to 50 C). The qualification of the ASIC is still pending. However, it is expected to be satisfactory attending previous experiences on ASICs of the same characteristics and designed in the same technology using RHDB techniques and the same Rad- Hard library.