TPS543320, TPS543620, TPS543820 Schematic and Layout Checklist May 2021

This checklist provides a comprehensive overview of the TPS543320, TPS543620, and TPS543820 schematic and layout guidelines for May 2021. It includes schematic notes, version history, best practices, and detailed descriptions of key components such as PGOOD, MODE, FB, AGND, BP5, BOOT, VIN, PGND, and more. Ensure proper connections and component ratings for optimal performance.

Download Presentation

Please find below an Image/Link to download the presentation.

The content on the website is provided AS IS for your information and personal use only. It may not be sold, licensed, or shared on other websites without obtaining consent from the author. If you encounter any issues during the download, it is possible that the publisher has removed the file from their server.

You are allowed to download the files provided on this website for personal or commercial use, subject to the condition that they are used lawfully. All files are the property of their respective owners.

The content on the website is provided AS IS for your information and personal use only. It may not be sold, licensed, or shared on other websites without obtaining consent from the author.

E N D

Presentation Transcript

TPS543320, TPS543620 & TPS543820 Schematic & Layout Checklist BSR-MV HC May 2021 1

Version History Version Number Version Number Release Date Release Date Comments Comments 1.0 May 2021 Initial Release 2

Agenda TPS543320, TPS543620 & TPS543820 Schematic Checklist TPS543320, TPS543620 & TPS543820 Layout Checklist Generic Best Practices for Schematics 3

TPS543320, TPS543620 & TPS543820 Schematic Checklist BSR-MV HC May 2021 4

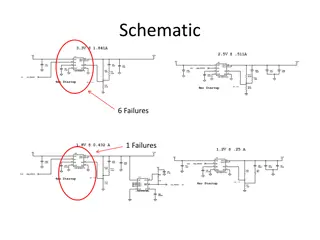

Schematic Overview PGOOD MODE FB 4 3 2 SYNC/ FSEL AGND 5 1 BP5 6 14 BOOT EN 7 13 SW Click the pin to go to the corresponding page VIN 8 12 VIN 10 PGND 9 11 PGND SW 5

Schematic Notes: VIN Rail #1 Rail #1 Rail #2 Rail #2 Rail #3 Rail #3 Two Two ceramic capacitors of at least 10 F capacitors of at least 0.1 F Decoupling capacitors are important for reducing the switch node ringing and FET robustness. Ceramic capacitors of type X5R, X7R, or similar are required. 10 F and two required. two high frequency ceramic bypass 0.1 F are required Some applications may require a bulk capacitor The ripple current rating of the input capacitors must be greater than the maximum RMS input current 6

Schematic Notes: BOOT Rail #1 Rail #1 Rail #2 Rail #2 Rail #3 Rail #3 Add a 0 0 resistor (place holder) in series with the boot capacitor To minimize SW ringing, RBOOT can be increased. Typically an RBOOT of 2.2 2.2 is used in high input voltage and high output current applications. In case of the 8 A application (TPS543820) and high input voltage (> 12 V), adding RBT is a must Use pin 13 (Not pin 10) for Bootstrap purposes Use a 0.1uF capacitor with at least 0.1uF X5R (X7R for high-temperature applications) bootstrap at least 10V rating. 7 7

Schematic Notes: BP5 Rail #1 Rail #1 Rail #2 Rail #2 Rail #3 Rail #3 A 2.2- F ceramic capacitor must be connected between the BP5 pin and AGND AGND for proper operation. The capacitor must be rated for at least 6.3 V and at least 0402 size to minimize DC bias derating. In TPS543X20 the BP5 can be connected to external supply of voltage 8

Schematic Notes: AGND Rail #1 Rail #1 Rail #2 Rail #2 Rail #3 Rail #3 Note which connections use AGND instead of PGND Ensure that separate symbols are used for AGND and PGND and the two nets connect at a single point 9 9

Schematic Notes: PGND Rail #1 Rail #1 Rail #2 Rail #2 Rail #3 Rail #3 Ensure that PGND is common ground for output capacitors, input capacitors Ensure that separate symbols are used for AGND and PGND and the two nets connect at a single point 10

Schematic Notes: Recommended AGND to PGND Connection Rail #1 Rail #1 Rail #2 Rail #2 Rail #3 Rail #3 The connection between AGND and PGND should be of a very low impedance impedance very low 11 11

Schematic Notes: FB Rail #1 Rail #1 Rail #2 Rail #2 Rail #3 Rail #3 Use a zero Ohms feed forward resistor in series with the feed forward capacitor (as a place holder) As an alternative, for better voltage regulation, use a 1 Kohms bottom resistor in the FB voltage divider The value of feed forward resistor (R3) should be smaller than 1/10 of the upper divider resistor (R7) For a quite feed back signal, connect the bottom feedback resistor (R8) directly to AGND pin at the top side (No via should be used) 12

Schematic Notes: SYNC/FSEL Rail #1 Rail #1 Rail #2 Rail #2 Rail #3 Rail #3 Connect RFSEL to quite AGND ground to select the desired switching frequency . Only one out of 5 predetermined frequencies can be selected by RFSEL. Alternatively the device can be synchronized to an external clock by applying a square wave clock signal to the SYNC/FSEL pin with a duty cycle from 20% to 80%. If SYNC/FSEL connected to an external clock, then Fsw could be set to any frequency in between the above predetermined frequencies, and not limited to the 5 above mentioned frequencies. Refer to Datasheet for more details 13

Schematic Notes: MODE Rail #1 Rail #1 Rail #2 Rail #2 Rail #3 Rail #3 The ramp amplitude, soft-start time, and current limit settings are programmed with a single resistor, RMODE, between MODE and AGND. The table lists the resistor values for the available options. It is required to use a 1% tolerance resistor or better. Refer to the Data-Sheet for the full table. Connect RMODE to quite AGND ground to select the desired configuration Ensure the proper Cramp is selected according to the guidance by the Datasheet or the Excel tool 14 14 14 14

Schematic Notes: EN Rail #1 Rail #1 Rail #2 Rail #2 Rail #3 Rail #3 Here, a resistor divider from VIN to AGND tapped to EN sets enable voltage to the desired level. A separate EN power source can also be used, note that EN is rated for 6V maximum 6V maximum. If a capacitor between EN and AGND is present, ensure that the RC time constant is small enough to avoid power up/power down timing issues. Determine which of these methods you will use for setting the EN pin voltage DO NOT DO NOT connect EN pin to VIN pin directly. Floating EN pin before startup enables the converter. 15

Schematic Notes: PGOOD Rail #1 Rail #1 Rail #2 Rail #2 Rail #3 Rail #3 PGOOD is open drain, requires By default, PGOOD is pulled low and this low-level output voltage is no more than 500-mV with 2mA sinking current. Once the FB pin is between 92% and 108% of the internal voltage reference, soft start is complete, and after a 256- s deglitch time, the PGOOD pin is de-asserted and the pin floats. Minimum 1 V VIN for valid PGOOD output Note that Enable with UVLO asserts PGOOD LOW LOW requires 10k to 100k pull 10k to 100k pull- -up resistor to BP5 up resistor to BP5 (<5.5V) 16 16 16

Output Capacitor Check Rail #1 Rail #1 Rail #2 Rail #2 Rail #3 Rail #3 Check output cap meets stability, ripple and transient requirements. Check ESR of non ceramic caps. Check DC voltage derating of ceramic caps (50% to 70% typical) Capacitors types of X5R or better should be used 17

Output Inductor Check Rail #1 Rail #1 Rail #2 Rail #2 Rail #3 Rail #3 Pin # 10 should be used as Switch Node that connects and drives the output inductor 18

Input Inductor Check Rail #1 Rail #1 Rail #2 Rail #2 Rail #3 Rail #3 If input LC is used, check to make sure the Q is properly dampened (Not shown here) 19

TPS543320, TPS543620 & TPS543820 Layout Checklist BSR-MV HC May 2021 20

Layout Notes: VIN Rail #1 Rail #1 Rail #2 Rail #2 Rail #3 Rail #3 Two Two 0402 high frequency ceramic bypass capacitors of at least 0.1 F should be placed as close as possible to the two VIN pins and be connected directly to the VIN pins through top layer traces (without use of any vias ) 0.1 F Additional two ceramic capacitors of at least 10 F required at the two sides of the chip, the placement these capacitors is not as critical, and these capacitors may even be placed at the other side of the PCB connecting through multiple vias 21

Layout Notes: BOOT Rail #1 Rail #1 Rail #2 Rail #2 Rail #3 Rail #3 Place the boot resistor (if used, not shown here) as close as possible close as possible to the BOOT pin, followed by the boot capacitor TI does NOT the BOOT path if there are concerns about EMI in your design. NOT recommend using vias on 22 22

Layout Notes: BP5 Rail #1 Rail #1 Rail #2 Rail #2 Rail #3 Rail #3 Place the BP5 decoupling capacitor (2.2uF/6.3V/X6S/0402 or 2.2uF/6.3V/X7R/0603) as close as possible possible to the device. as close as Ensure the BP5 decoupling loop is minimized. Do NOT NOT use vias in the BP5 path. BP5 is the supply for internal control circuitry; taking these steps minimizes the noise. 23

Layout Notes: SW Rail #1 Rail #1 Rail #2 Rail #2 Rail #3 Rail #3 Ensure that the SW PCB trace is as short and wide as possible as short and wide as possible to minimize parasitic inductance & capacitance, as well as noise coupling. 24

Layout Notes: PGND Rail #1 Rail #1 Rail #2 Rail #2 Rail #3 Rail #3 Use as many Use as many PGND vias as possible on both sides of the chip and as close as possible possible to the PGND pins. This is required in order to minimize parasitic impedance and lower thermal resistance. as close as Have a large solid ground large solid ground plane plane for PGND. Maximize the PGND surface area on the outer layers to maximize heat dissipation 25

Layout Notes: FB Rail #1 Rail #1 Rail #2 Rail #2 Rail #3 Rail #3 Place the feedback resistor near the device the device to minimize the FB trace distance. This is to minimize noise, as FB is a high- impedance node. near Ensure that noisy signals are not routed near power planes to minimize noise on the output. 26

Recommended AGND to PGND Connection Rail #1 Rail #1 Rail #2 Rail #2 Rail #3 Rail #3 VIN and VOUT are referenced to PGND, analog FB, BP5 and the rest of the signals are referenced to AGND The connection between AGND and PGND should be of a very low impedance impedance very low Consider the BP5 capacitor as the boarder line between AGND and PGND. The connection between AGND and PGND should be close to BP5 capacitor and the IC, but at further side of BP5 capacitor only, the side that is further away from the chip and the AGND pin 27

Best Practices for a smooth and quick Schematic/Layout review BSR-MV HC May 2021 28

U1 SPECIFICATION INPUT VOLTAGE: 12V OUTPUT VOLTAGE: 2.5V OUTPUT LOAD CURRENT: 15A OUTPUT VOLTAGE RIPPLE: 10mVpp OUTPUT VOLTAGE UNDER/OVERSHOOT AFTER LOAD STEP: 50mV OUTPUT OVERCURRENT: 15A SOFT-START TIME: 5.5ms SWITCHING FREQUENCY: 0.8MHz OPERATING MODE: Skip-Mode OPERATING TEMPERATURE: 25 C Generic Best Practices for Schematics (1/5) Add text for expected currents and voltages near input and output terminals If pins are connected to off sheet supply, note the voltage level. 12V Check standardized Info Note 4.5V 2.5V, 15A GRM188R60J476ME15J Add text for significant off-page components (eg. output capacitors) No 4-way ties Different ground symbols for quiet and power ground Ground symbols should point down 29

U1 SPECIFICATION INPUT VOLTAGE: 12V OUTPUT VOLTAGE: 2.5V OUTPUT LOAD CURRENT: 15A OUTPUT VOLTAGE RIPPLE: 10mVpp OUTPUT VOLTAGE UNDER/OVERSHOOT AFTER LOAD STEP: 50mV OUTPUT OVERCURRENT: 15A SOFT-START TIME: 5.5ms SWITCHING FREQUENCY: 0.8MHz OPERATING MODE: Skip-Mode OPERATING TEMPERATURE: 25 C Generic Best Practices for Schematics (2/5) Check input cap meets bypass and ripple requirements Note part number or value, rdc and Irms, isat rating of inductor 12V 4.5V 2.5V, 15A GRM188R60J476ME15J Note part number or value, esr and voltage rating, dielectric for capacitors Check FB network is correct (including feedforward cap, external ripple injection and any external margining circuits) 30

Generic Best Practices for Schematics (3/5) Check other feature settings (adjustable current limit, adjustable ss, adjustable uvlo) Make sure all pins on a device are present on a device symbol Note NoPop and DNI components Note power sequencing Generated .pdf are better than scanned .pdf for using Ctrl-F to find the devices and net in large schematics Provide a searchable format and/or help point to guide us to look at specific part that contains the regulator circuitry 31

Important notice and disclaimer TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES AS IS AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS. These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources. TI s products are provided subject to TI s Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI s provision of these resources does not expand or otherwise alter TI s applicable warranties or warranty disclaimers for TI products. 32