Troubleshooting DCLK Divider Configuration Challenges in FPGA Setup

Discover solutions for configuring the DCLK Divider in an FPGA setup to achieve the desired output frequencies with input PLL reference clocks. Explore images detailing the settings for different divider values and their corresponding output frequencies.

Download Presentation

Please find below an Image/Link to download the presentation.

The content on the website is provided AS IS for your information and personal use only. It may not be sold, licensed, or shared on other websites without obtaining consent from the author. If you encounter any issues during the download, it is possible that the publisher has removed the file from their server.

You are allowed to download the files provided on this website for personal or commercial use, subject to the condition that they are used lawfully. All files are the property of their respective owners.

The content on the website is provided AS IS for your information and personal use only. It may not be sold, licensed, or shared on other websites without obtaining consent from the author.

E N D

Presentation Transcript

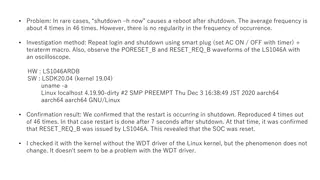

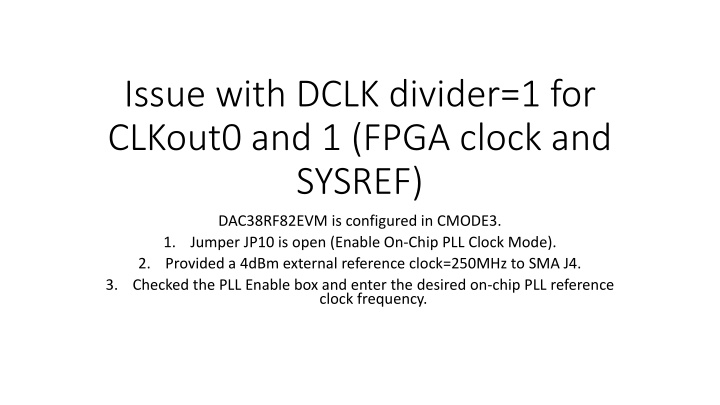

Issue with DCLK divider=1 for CLKout0 and 1 (FPGA clock and SYSREF) DAC38RF82EVM is configured in CMODE3. 1. Jumper JP10 is open (Enable On-Chip PLL Clock Mode). 2. Provided a 4dBm external reference clock=250MHz to SMA J4. 3. Checked the PLL Enable box and enter the desired on-chip PLL reference clock frequency.

We are changing DCLK Divider (CLKout 0 and 1) in LMK04828.

DCLK Divider=1 Input PLL ref clock is 250MHz and Output frequency is not 250MHz for this case. Output frequency is not 250MHz for this case.

DCLK Divider=2 Input PLL ref clock is 250MHz and Output frequency is 125MHz for this case

DCLK Divider=3 Input PLL ref clock is 250MHz and Output frequency is 83.33MHz for this case

DCLK Divider=4 Input PLL ref clock is 250MHz and Output frequency is 62.5MHz for this case

DCLK Divider=5 Input PLL ref clock is 250MHz and Output frequency is 50MHz for this case

DCLK Divider=2 Input PLL ref clock is 500MHz and Output frequency is 250MHz for this case