Understanding Memory Functions in CPU Processing

Explore the intricate workings of CPU memory devices, addressing, storing data, loading, and control mechanisms. Learn about various data types, address values, and storage processes involved in memory operations. Experience a visual journey through slides depicting memory read and write sequences, byte handling, and operational loads. Delve into the complexities of data processing, memory control, and IRQ operations within a CPU system.

Download Presentation

Please find below an Image/Link to download the presentation.

The content on the website is provided AS IS for your information and personal use only. It may not be sold, licensed, or shared on other websites without obtaining consent from the author. If you encounter any issues during the download, it is possible that the publisher has removed the file from their server.

You are allowed to download the files provided on this website for personal or commercial use, subject to the condition that they are used lawfully. All files are the property of their respective owners.

The content on the website is provided AS IS for your information and personal use only. It may not be sold, licensed, or shared on other websites without obtaining consent from the author.

E N D

Presentation Transcript

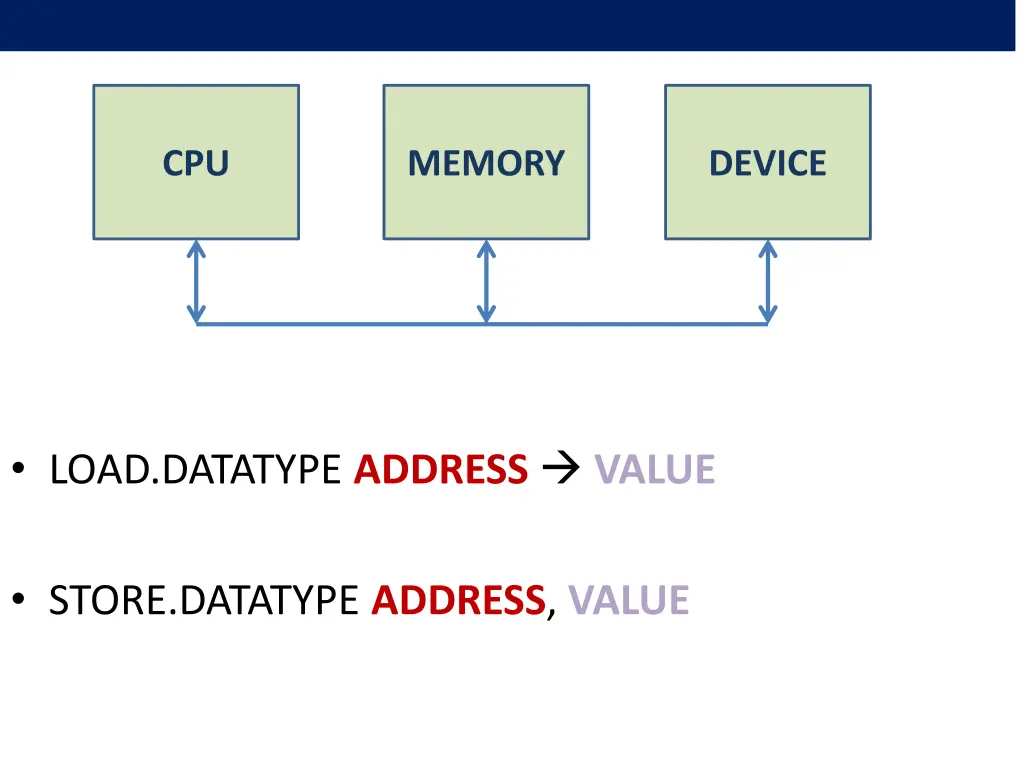

CPU MEMORY DEVICE LOAD.DATATYPE ADDRESS VALUE STORE.DATATYPE ADDRESS, VALUE

32 ADDRESS Address A31-A0 8 DataOut Do7-Do0 DATA To Memory and Devices 8 DataIn Di7-Di0 Processor R/W ME CONTROL` ACK 32 IRQ IRQ31-IRQ0

MEMORY READ #1 32 ADDRESS Address A31-A0 8 DataOut Do7-Do0 DATA To Memory and Devices 8 DataIn Di7-Di0 Processor R/W ME CONTROL` ACK 32 IRQ IRQ31-IRQ0

MEMORY READ #2 32 ADDRESS Address A31-A0 8 DataOut Do7-Do0 DATA To Memory and Devices 8 DataIn Di7-Di0 Processor R/W ME CONTROL` ACK 32 IRQ IRQ31-IRQ0

MEMORY WRITE #1 32 ADDRESS Address A31-A0 8 DataOut Do7-Do0 DATA To Memory and Devices 8 DataIn Di7-Di0 Processor R/W ME CONTROL` ACK 32 IRQ IRQ31-IRQ0

MEMORY WRITE #2 32 ADDRESS Address A31-A0 8 DataOut Do7-Do0 DATA To Memory and Devices 8 DataIn Di7-Di0 Processor R/W ME CONTROL` ACK 32 IRQ IRQ31-IRQ0

BYTES, HALF-WORDS, WORDS 30 ADDRESS Address A31-A2 32 DataOut Do31-Do0 DATA To Memory and Devices 32 DataIn Di31-Di0 Processor 4 ByteEnable R/W ME CONTROL` ACK 32 IRQ IRQ31-IRQ0

BE0 BE1 BE2 BE3 D0 D7 D8 D15 D15 D23 D24 D31 x x00 x x01 x x10 x x11 x x00 x x10 x x00

Operation LOAD.WORD 10000 LOAD.HWORD 10000 LOAD.HWORD 10010 LOAD.BYTE 10000 LOAD.BYTE 10001 LOAD.BYTE 10010 LOAD.BYTE 10011 LOAD.BYTE 11010 LOAD.BYTE 11101 A31-A2 0 0100 0 0100 0 0100 0 0100 0 0100 0 0100 0 0100 0 0110 0 0111 BE3-BE0 1111 0011 1100 0001 0010 0100 1000 0100 0010

MEMORY READ #1 30 ADDRESS Address A31-A2 32 DataOut Do31-Do0 DATA To Memory and Devices 32 DataIn Di31-Di0 Processor 4 ByteEnable R/W ME CONTROL` ACK 32 IRQ IRQ31-IRQ0

MEMORY READ #2 30 ADDRESS Address A31-A2 32 DataOut Do31-Do0 DATA To Memory and Devices 32 DataIn Di31-Di0 Processor 4 ByteEnable R/W ME CONTROL` ACK 32 IRQ IRQ31-IRQ0

MEMORY WRITE #1 30 ADDRESS Address A31-A2 32 DataOut Do31-Do0 DATA To Memory and Devices 32 DataIn Di31-Di0 Processor 4 ByteEnable R/W ME CONTROL` ACK 32 IRQ IRQ31-IRQ0

MEMORY WRITE #2 30 ADDRESS Address A31-A2 32 DataOut Do31-Do0 DATA To Memory and Devices 32 DataIn Di31-Di0 Processor 4 ByteEnable R/W ME CONTROL` ACK 32 IRQ IRQ31-IRQ0

.text movhi r8, r0, %hi(0x200000) ori r8, r8, %lo(0x200000) ldh r9, 2(r8) addi r9, r9, 1 sth r9, 0(r8) assume it s @ 0x1000 I1: I2: I3: I4: I5: Load.word 0x1000 Load.word 0x1004 Load.word 0x1008 Load.hword 0x200002 Load.word 0x100c Load.word 0x1010 Store.hword 0x200000, value fetch I1 fetch I2 fetch I3 ldh r9, 2(r8) fetch I4 fetch I5 sth r9, 0(r8)

Load.word 0x1000 30 Address A31-A2 = 0000 0000 0000 0000 0001 0000 0000 00 32 DataOut Do31-Do0 32 DataIn Di31-Di0 = Processor 4 ByteEnable = 1 R/W = 1 ME = 1 ACK 32 IRQ IRQ31-IRQ0

Load.word 0x1000 30 Address A31-A2 = 0000 0000 0000 0000 0001 0000 0000 00 32 DataOut Do31-Do0 DataIn Di31-Di0 = movhi r8, r0, %hi(0x200000) 32 Processor 4 ByteEnable = 1 R/W = 1 ME = 1 ACK = 1 32 IRQ IRQ31-IRQ0

CONNECTING MULTIPLE DEVICES 30 Address A31-A2 32 DataOut Do31-Do0 32 DataIn Di31-Di0 Processor 4 ByteEnable R/W ME ACK 32 IRQ IRQ31-IRQ0

CONNECTING MULTIPLE DEVICES 30 Address A31-A2 32 DataOut Do31-Do0 32 DataIn Di31-Di0 Processor 4 ByteEnable R/W ME ACK 32 IRQ IRQ31-IRQ0

CONNECTING MULTIPLE DEVICES 30 Address A31-A2 32 DataOut Do31-Do0 32 DataIn Di31-Di0 Processor 4 ByteEnable R/W ME ACK 32 IRQ IRQ31-IRQ0

CONNECTING MULTIPLE DEVICES 30 Address A31-A2 DataOut Do31-Do0 32 32 Data D31-D0 4 32 ByteEnable DataIn Di31-Di0 R/W ME ACK Processor 32 IRQ IRQ31-IRQ0

A Write I/O Register STORE.WORD 0x00300000, 0xfabfadad 32 A31-A0 8 Do7-Do0 8 Di7-Di0 D0-D31 Processor BE 4 R/W ME W ACK IRQ IRQ31-IRQ0 32

A Write I/O Register STORE.WORD 0x00300000, 0xfabfadad 32 A31-A0 8 Do7-Do0 8 Di7-Di0 D0-D31 Processor BE 4 R/W 0 STORE ME 1 W ACK IRQ IRQ31-IRQ0 32

A Write I/O Register STORE.WORD 0x00300000, 0xfabfadad 32 A31-A0 8 Do7-Do0 8 Di7-Di0 D0-D31 Processor BE WORD 4 R/W STORE ME 1 W ACK IRQ IRQ31-IRQ0 32

A Write I/O Register STORE.WORD0x00300000, 0xfabfadad 32 == 0x30 0000 (upper 32 bits) A31-A0 8 Do7-Do0 8 Di7-Di0 D0-D31 Processor BE WORD 4 R/W STORE ME 1 W ACK IRQ IRQ31-IRQ0 32

A Write I/O Register STORE.WORD0x00300000, 0xfabfadad 32 == 0x30 0000 (upper 32 bits) A31-A0 8 Do7-Do0 8 Di7-Di0 D0-D31 Processor BE WORD 4 R/W STORE ME 1 W ACK IRQ IRQ31-IRQ0 32

A Write I/O Register STORE.WORD0x00300000, 0xfabfadad 32 == 0x30 0000 (upper 32 bits) A31-A0 8 Do7-Do0 8 Di7-Di0 D0-D31 Processor BE WORD 4 R/W 0 STORE ME 1 W ACK IRQ IRQ31-IRQ0 32

A Write I/O Register STORE.WORD0x00300000, 0xfabfadad 32 == 0x30 0000 (upper 32 bits) A31-A0 8 Do7-Do0 8 Di7-Di0 D0-D31 Processor BE WORD 4 R/W 0 STORE ME 1 W ACK 1 IRQ IRQ31-IRQ0 32

Word address match STORE.WORD0x00300000, 0xfabfadad A31-A2 = 0000 0000 0011 0000 0000 0000 0000 0000

A Read I/O Register STORE.WORD 0x00300000, 0xfabfadad 32 A31-A0 8 Do7-Do0 8 Di7-Di0 D0-D31 Processor BE 4 R/W ME R ACK IRQ IRQ31-IRQ0 32