Verilog Review and Advance Speaker: Fu-Sheng Yu - Media IC & System Lab

In the Media IC and System Lab at the Graduate Institute of Electronics Engineering, National Taiwan University, various topics related to Verilog, hardware design flow, RTL coding, gate-level design, and simulation are covered. The lab's focus includes circuit abstraction, synthesis, timing analysis, and common issues in IC design. Fu-Sheng Yu serves as a speaker in advancing Verilog understanding and implementation. The lab provides valuable insights into cell-based IC design, design flows, and hardware technologies, aiding students in mastering advanced topics in electronics engineering and integrated circuit design.

Download Presentation

Please find below an Image/Link to download the presentation.

The content on the website is provided AS IS for your information and personal use only. It may not be sold, licensed, or shared on other websites without obtaining consent from the author.If you encounter any issues during the download, it is possible that the publisher has removed the file from their server.

You are allowed to download the files provided on this website for personal or commercial use, subject to the condition that they are used lawfully. All files are the property of their respective owners.

The content on the website is provided AS IS for your information and personal use only. It may not be sold, licensed, or shared on other websites without obtaining consent from the author.

E N D

Presentation Transcript

Media IC and System Lab Graduate Institute of Electronics Engineering National Taiwan University Verilog Review and Advance Speaker: Fu-Sheng Yu ( ) Media IC & System Lab 1

Outline Design flow overview Verilog basic introduction Hardware advance topic Media IC & System Lab 2

HDL vs Software Language Media IC & System Lab 3

Cell-Based IC Design Specifications RTL Coding RTL code Front-End Synthesis Gate-level netlist DFT Insertion ATPG Place and Route Test Patterns DRC LVS GDS Layout Back-End Layout Tape Out Media IC & System Lab 4

Circuit Abstraction Media IC & System Lab 5

RTL simulation Testbed.v Design.v Media IC & System Lab 6

Common issues ncverilog testbed.v design.v +access+r to dump waveform +notimingcheck if using SRAM $fsdbDumpvars(0,"+mda") to dump all memory signal, including 2D array Media IC & System Lab 7

Synthesis Map your RTL code to standard cell Optimization to meet timing constraint Static timing analysis (STA) Media IC & System Lab 8

RTL vs Gate-Level RTL sel 1 in2 out in1 0 Gate-level a2_o in2 a2 out in1 o1 a1_o iv_sel a1 sel n1 Media IC & System Lab 9

Gate-level simulation Use the same pattern in RTL simulation Dynamic timing analysis (DTA) Media IC & System Lab 10

Outline Design flow overview Verilog basic introduction Hardware advance topic Media IC & System Lab 11

Combinational & Sequential Sequential Part Combinational Part in1 sel 1 out clk 0 in2 clk Memory-less Always running clk Media IC & System Lab 12

Sequential Part Describe the behavior of sequential circuit always @ ( <sensitivity edge > <clock> [or <sensitivity edge> < reset >] ) if ( reset ) ; // reset mode else ; // normal mode Asynchronous reset Synchronous reset rst D Q next_count count clk Media IC & System Lab 13

Asynchronous & synchronous reset Asyn reset reset at the posedge of reset signal Syn reset reset at the posedge of clock signal Syn reset no reset occurs Media IC & System Lab 14

Metastability The unstable status due to non ideal data transition is called metastability. Media IC & System Lab 15

Setup time & Hold time Setup time(Tsu) : the minimum amount of time the data signal should be held steady before the clock. Hold time (Th) : the minimum amount of time the data signal should be held steady after the clock Media IC & System Lab 16

Critical Path Critical path is the path that has longest delay between reg or in/out in the whole circuit. Delay: 5ns Delay: 3ns clk clk clk Media IC & System Lab 17

Pipeline Delay: 4ns Delay: 4ns clk clk Delay: 4ns Delay: 4ns clk clk clk Media IC & System Lab 18

Input buffer Input Delay 4ns Delay: 4ns clk Input Delay 4ns Delay: 4ns clk clk Media IC & System Lab 19

Clear control Circuit Controlling Unit Processing Unit Media IC & System Lab 20

Finite State Machine (FSM) IDLE down =1 ZERO DOWN count=0 Media IC & System Lab 21

Behavior Modeling of FSM Combinational Part Next-state logic (NL) Output logic (OL) Sequential Part Current state (CS) stored in flip-flops 3 Coding Style Separate CS, OL and NL Combine NL+ OL, separate CS Combine CS + NL, separate OL Media IC & System Lab 22

Coding Style 1: Separate CS, OL and NL Media IC & System Lab 23

Code Sample of FSM Media IC & System Lab 24

Code Sample of FSM Media IC & System Lab 25

Finite State Machine (FSM) Media IC & System Lab 26

Common issues Data type reg is NOT definitely to be a register. Instead, the synthesis result depends on the described behavior of RTL. Multiple Driven Signals issue The variable of data type wire can NOT be repeatedly assigned. The variable of data type reg can only be assigned in single always block. x x Media IC & System Lab 27

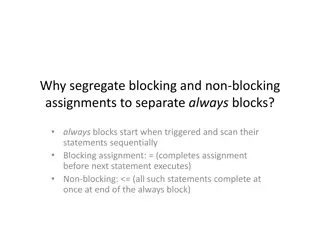

Common issues Avoid appearance of Latch during synthesis. Latch is too advanced for beginner of digital circuit. Latch is due to incomplete assignment in combinational part. Incomplete assignment implies that circuit will hold the previous Usage of positive & negative clock simultaneously is NOT recommended. Timing issue will cause the poor performance if not design properly. Complicated clock tree for skew issue during place and route. Media IC & System Lab 28

Outline Design flow overview Verilog basic introduction Hardware advance topic Design ware Memory System verilog Media IC & System Lab 29

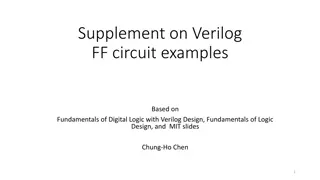

Design ware IP(Intellectual Property) Hard IP: GDSII format Firm IP: Netlist resource Soft IP: RTL design In Media 11 Datasheet and manual are in /opt/CAD/synopsys/synthesis/2019.12/dw/doc/ Media IC & System Lab 30

Design ware RTL behavior simulation Absolute path: `include /opt/CAD/synopsys/synthesis/2019.12/dw/sim_ver/DW_sqrt.v" Relative path: `include "DW_sqrt.v ncverilog tb.v design.v -incdir /opt/CAD/synopsys/synthesis/2019.12/dw/sim_ver/ Synthesis Usage Media IC & System Lab 31

Memory Media IC & System Lab 32

SRAM Slower but has less area than register Only one address can be accessed in same time(single port SRAM) Media IC & System Lab 33

DRAM Off chip memory, Read/Write latency penalty is huge Data burst Media IC & System Lab 34

SystemVerilog - Logic data type Reason: The datatype isn t equal to the real circuit. reg doesn t mean a register. It depends on how you use these variables. So, in SystemVerilog, a new type logic is introduced to replace both of them. reg for procedural assignment (within always block) Flip-Flop must be the data type of reg wire for continuous assignment (assign) module MyModule( input wire a, output reg b, input wire c, output wire d, module MyModule( input logic a, output logic b, input logic c, output logic d, Media IC & System Lab 35

SystemVerilog - always blocks Replace all always@(*) by always_comb Replace sequential always block by always_ff Media IC & System Lab 36

SystemVerilog - Enum & unique case Media IC & System Lab 37

SystemVerilog - type define Media IC & System Lab 38

Reference Slide from Hung-Chang Lu Slide from Shao-Syuan Huang Slide from NTU CVSD course Slide from NCTU ICLAB course Media IC & System Lab 39