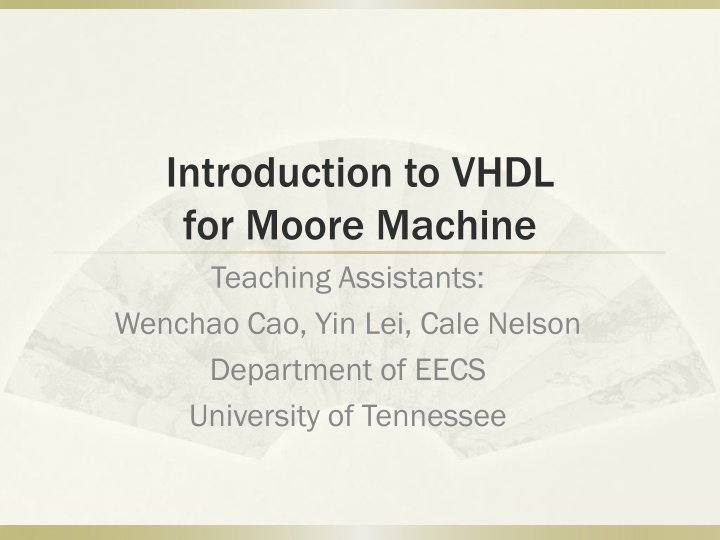

VHDL Introduction for Moore Machine Teaching Assistants

Explore VHDL concepts for Moore and Mealy machines, learn through examples, and understand VHDL syntax and architecture for Moore machines. Dive into type declarations and more in this helpful guide for teaching assistants.

Download Presentation

Please find below an Image/Link to download the presentation.

The content on the website is provided AS IS for your information and personal use only. It may not be sold, licensed, or shared on other websites without obtaining consent from the author. If you encounter any issues during the download, it is possible that the publisher has removed the file from their server.

You are allowed to download the files provided on this website for personal or commercial use, subject to the condition that they are used lawfully. All files are the property of their respective owners.

The content on the website is provided AS IS for your information and personal use only. It may not be sold, licensed, or shared on other websites without obtaining consent from the author.

E N D

Presentation Transcript

Introduction to VHDL for Moore Machine Teaching Assistants: Wenchao Cao, Yin Lei, Cale Nelson Department of EECS University of Tennessee

Moore Machine and Mealy Machine Moore machine: Moore machine: Each Each node (state) is labeled with an output node (state) is labeled with an output value. value. Input State / Output State / Output Mealy machine: Mealy machine: Each Each arc (transition) is labeled with an output value. arc (transition) is labeled with an output value. Input / Output State State

Example of Moore Example of Moore Machine Machine Example of Moore machine Example of Moore machine Three inputs: Reset, CLK, w One outpu: z Four states: S0, S1, S2, S3 Reset Moore FSM w z CLK w = 1 Reset = 0 w = 0 S0 / z = 0 S1 / z = 1 w = 1 w = 0 w = 1 w = 0 w = 0 w = 1 S3 / z = 1 S2 / z = 0

Example of VHDL for Moore Machine w = 1 Reset = 0 w = 0 S0 / z = 0 S1 / z = 1 w = 1 w = 0 w = 1 VHDL Syntax : VHDL Syntax : Entity Entity w = 0 w = 0 w = 1 S3 / z = 1 S2 / z = 0 entity <entity_name> is port( port assignments ... ); end [entity | <entity_name>];

Example of VHDL for Moore Machine w = 1 Reset = 0 w = 0 S0 / z = 0 S1 / z = 1 VHDL Syntax : Architecture VHDL Syntax : Architecture w = 1 w = 0 w = 1 w = 0 w = 0 architecure <architecture_name> of <entity_name> is [ component declarations function declarations signal declarations constant declarations variable declarations type declarations ... ] begin [ combinatorial statements sequential statements ... ] end architecture; w = 1 S3 / z = 1 S2 / z = 0

Example of VHDL for Moore Machine w = 1 Reset = 0 w = 0 S0 / z = 0 S1 / z = 1 VHDL Syntax : VHDL Syntax : Type declarations Type declarations w = 1 w = 0 w = 1 w = 0 w = 0 w = 1 S3 / z = 1 S2 / z = 0 type <type_name> is (<values>); -- where values is a list of acceptable values -- array types can be defined as follows: type <type_name> is array (<low> to <high>) of <data_type>; type <type_name> is array (<high> downto <low>) of <data_type>;

Example of VHDL for Moore Machine w = 1 Reset = 0 w = 0 S0 / z = 0 S1 / z = 1 VHDL Syntax : VHDL Syntax : Signal declarations Signal declarations w = 1 w = 0 w = 1 w = 0 w = 0 w = 1 S3 / z = 1 S2 / z = 0 Signals are declared outside the process using the following statement: signal signal list_of_signal_names: type [ := initial value] ; signal signal SUM, CARRY: std_logic; signal signal CLOCK: bit; signal signal TRIGGER: integer :=0; signal signal DATA_BUS: bit_vector (0 to 7); signal signal VALUE: integer range range 0 to to 100;

Example of VHDL for Moore Machine VHDL Syntax : VHDL Syntax : Processes Processes [<process_name>:] process (<sensitive signals>) variable declarations constant declarations ... begin statements ... end process; w = 1 Reset = 0 w = 0 S0 / z = 0 S1 / z = 1 w = 1 w = 0 w = 1 w = 0 w = 0 w = 1 S3 / z = 1 S2 / z = 0

Example of VHDL for Moore Machine VHDL Syntax : VHDL Syntax : If If- -Then Then- -Else statement Else statement if <condition> then statements ... [ elsif <condition> then statements ... else statements ... ] endif; w = 1 Reset = 0 w = 0 S0 / z = 0 S1 / z = 1 w = 1 w = 0 w = 1 w = 0 w = 0 w = 1 S3 / z = 1 S2 / z = 0

Example of VHDL for Moore Machine VHDL Syntax : Signal attributes VHDL Syntax : Signal attributes One of the signal attributes: One of the signal attributes: signal_name event Function: Function: returns the Boolean value True if an event on the signal occurred, otherwise gives a False Example: Example: if (CLOCK eventand CLOCK= 1 ) then This expression checks for the arrival of a positive clock edge. w = 1 Reset = 0 w = 0 S0 / z = 0 S1 / z = 1 w = 1 w = 0 w = 1 w = 0 w = 0 w = 1 S3 / z = 1 S2 / z = 0

Example of VHDL for Moore Machine VHDL Syntax : Case statement VHDL Syntax : Case statement case <expression> is when <choice(s)> => <expression>; ... when ... [when others => ... ] end case; w = 1 Reset = 0 w = 0 S0 / z = 0 S1 / z = 1 w = 1 w = 0 w = 1 w = 0 w = 0 w = 1 S3 / z = 1 S2 / z = 0

Example of VHDL for Moore Machine w = 1 Reset = 0 w = 0 S0 / z = 0 S1 / z = 1 w = 1 w = 0 w = 1 w = 0 w = 0 w = 1 S3 / z = 1 S2 / z = 0

References http://webdocs.cs.ualberta.ca/~amaral/courses/329/labs/VHDL_Refe rence.html#signal_dec http://www.seas.upenn.edu/~ese171/vhdl/vhdl_primer.html#_Toc526 061362 http://www.ics.uci.edu/~jmoorkan/vhdlref/cases.html http://web.engr.oregonstate.edu/~traylor/ece474/vhdl_lectures/essen tial_vhdl_pdfs/essential_vhdl107-127.pdf http://www.gmvhdl.com/process.htm http://www.gmvhdl.com/signals.htm