Amplifier Design Tradeoffs in Transistor Operation

In the realm of electrical and computer engineering at Iowa State University, the design of amplifiers based on two-stage configurations is explored. The sensitivity of parameters like Idu=Id/(W/L) to VG and Vbs is investigated, shedding light on the tradeoff between weak, moderate, and strong inversion in transistor operation. By examining gm/Id vs. VG and the product of gm/Id and fT, optimal operating conditions are identified for speed and power efficiency considerations. The significance of the gm/id method in achieving better design accuracy, reducing uncertainties, and facilitating parameter determination is underscored.

Download Presentation

Please find below an Image/Link to download the presentation.

The content on the website is provided AS IS for your information and personal use only. It may not be sold, licensed, or shared on other websites without obtaining consent from the author.If you encounter any issues during the download, it is possible that the publisher has removed the file from their server.

You are allowed to download the files provided on this website for personal or commercial use, subject to the condition that they are used lawfully. All files are the property of their respective owners.

The content on the website is provided AS IS for your information and personal use only. It may not be sold, licensed, or shared on other websites without obtaining consent from the author.

E N D

Presentation Transcript

Amplifier Design ????based Two-Stage Chongli Cai IOWA STATE UNIVERSITY Department of Electrical and Computer Engineering

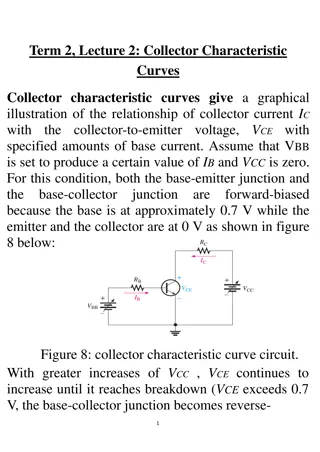

Motivation Idu=Id/(W/L) vs VG is sensitive to Vbs IOWA STATE UNIVERSITY Department of Electrical and Computer Engineering

Motivation gm/Id vs VG is also sensitive to Vbs IOWA STATE UNIVERSITY Department of Electrical and Computer Engineering

Motivation But gm/ID vs Idu=ID/(W/L) has fixed shape the gm/id value is fixed regardless of the transistor length With a certain current density, Let s look at the model we are using IOWA STATE UNIVERSITY Department of Electrical and Computer Engineering

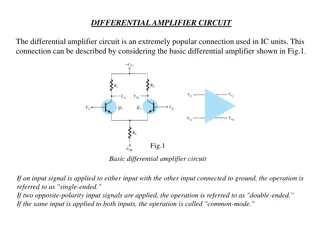

???? and ?? Design Tradeoff: Weak Inversion gm/Id Moderate Inversion Strong Inversion fT L=0.6um L=1.2um L=1.8um Vod Weak inversion: Large gm/Id(>20S/A), but small fT Strong inversion: Small gm/Id(<5S/A), but large fT IOWA STATE UNIVERSITY Department of Electrical and Computer Engineering

???? and ?? Product of (gm/Id)*fT Moderate Inversion L=0.6um L=1.2um Strong Inversion L=1.8um Weak Inversion Vod The product of gm/Id and fT peaks in moderate inversion Operating the transistor in moderate inversion is optimal when we value speed and power efficiency equally. But not always the case ! IOWA STATE UNIVERSITY Department of Electrical and Computer Engineering

???? is important ? Why - Better match to the fabricated one gm/id curve is generated from SPICE simulation, which is linked to the actual measurement data - Avoid the design uncertainties gm/id value does not rely on any model equation gm /id value has fixed shape regardless of transistor length and body bias gm/id curve is valid over all transistor operating ranges - Once selecting one point from gm/id curve, with another design parameter the third parameter can be easily determined - Example: gm/id method can reduce the design and optimization effort a lot W L I g I I I I W L m d I g d D m du du D IOWA STATE UNIVERSITY Department of Electrical and Computer Engineering

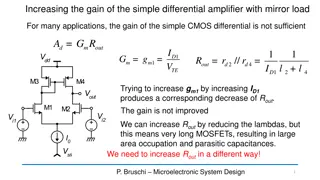

???? related to Design Specification ? V How DD Design Specification GBW, SR, phase margin, power and area etc 2 1 1 ( )*( ) ( 2 2 D c I C M 5 M M 8 7 g I g I 2D I C = = = GBW ) SR SR m 1 D 1 m 1 1 I 1 D 1 c V M M V + in C 2 I 1 in V c SR D + 6 out II I C C bias L c C L M + + C C C C C C C g / g m I I g / g m I I M M 4 = 1 1 6 PM 90 tan [( )( )( )] tan [( )( )] L o 1 L c c o 1 m 1 D 1 D 1 m 1 D 1 D 1 3 2 /I I /I I 6 D 6 D 6 c 6 D 6 D 6 V ss operating in the moderate inversion. So it is valid to assume ?o1 is smaller than ?? in the design. You will not gain more benefits on making M6 much larger It is better to select the gm/id value of M6 to make it g C g C = z m 6 = GBW m 1 1 c c 2 g C I = z m 3 = SR 5 2 C m c GBW GBW z g g g C The PM can be simplified as 90 tan [( PM = 1 1 PM 90 tan [ ] tan ( ) p o 1 o 1 |p2| 1 m 6 c g / g m I I C C g / g m I I 1 1 )( )( )] tan [( )( )] m 1 D 1 D 1 L m 1 D 1 D 1 g C C C + p m 6 c /I I /I I 2 + 6 D 6 D 6 c 6 D 6 D 6 C C g C C C L o 1 L c c o 1 g / g m I = Note : k m 1 D 1 = p m 3 /I 3 6 D 6 m I C C I = 1 1 PM 90 tan ( * k * ) tan ( * k ) D 1 L D 1 I I D 6 c D 6 IOWA STATE UNIVERSITY Department of Electrical and Computer Engineering

???? related to Design Specification ? How V C C C C I I I I Phase Margin = 60 DD + k (1 )( ) L D 1 1 3 = = M tan30 c D 6 I C C I 5 M M = 1 1 PM 90 tan ( * k * ) tan ( * k ) D 1 L D 1 8 7 2 2 1 k ( )( ) L D 1 I I D 6 c D 6 c D 6 V M M V + in C 2 C I I 1 in V c SR SR (1) c + D 1 out with the condition of I II I 2( C C ) bias D 6 L c C L M M M 4 6 3 C C I I C C I I + = 2 2 3 (1 k )( ) 1 k ( )( ) (2) L D 1 L D 1 c D 6 c D 6 V ss g I 2 GBW SR k is determined by the gm/Id value of M1 and M6 you choose Id1/Id6 can be determined in terms of total power consumption Once k and current ratio are chosen, then Cc is determined You need to use (1) to check the validity of the calculated Cc from (2) You need to keep observing the parasitic cap at gate of M6 to make sure it is small = m 1 D 1 2D I C = SR 1 I c I SR D + 6 II C C L I c g / g m = k m 1 D 1 /I 6 D 6 IOWA STATE UNIVERSITY Department of Electrical and Computer Engineering

Design Guideline Amplifier Design Procedure Step 0: noice gm1, SRII ID2 Gain-Bandwidth Requirement SR Specification g I 1( 2 = GBW ) SR m 1 Step 1: Choose ??1/??1 Step 2: Choose ??6/??6 D 1 g / g m I = k m 1 D 1 SR and Power Specification /I 6 D 6 C I I Step3: Choose ?D1/??6 c + D 1 2( C C ) PM Specification D C C 6 L c I I C C C C I I Step 4: Calculate Cc + = 2 2 3 (1 k )( ) 1 k ( )( ) L D 1 L D 1 SR Specification c D 6 c D 6 I I Step 5: Check the validity of Cc c + D 1 V 2( C ) DD D 6 L c M I I W L I I W L Step 6: Size M1 & M6 5 M = M ( ) D 1 = ( ) D 6 8 7 1 6 du 1 du 6 Step 7: Size M3 & M4 V M M V + in C 2 1 in V c out Step 8: Size M5 & M7 I bias C L M M M 4 6 3 V ss IOWA STATE UNIVERSITY Department of Electrical and Computer Engineering

Design Example Specification Specs Specification Supply Voltages +/- 2.5V Load Capacitor 2pF Total Current <=100uA DC Gain 75dB Gain-bandwidth-product 25MHz Phase Margin 60 Slew Rate 25MV/s IOWA STATE UNIVERSITY Department of Electrical and Computer Engineering

Design Step 1 to Step 5 g I 1( 2 = GBW ) SR m 1 V DD D 1 M gm1/id1 can result in GBW over-designed For GBW is barely at target value, choosing small gm1/ id1 can result in SR over-designed You can choose the gm1/id to make GBW and SR barely satisfy the target For SR is barely at target value, choosing a large 5 M M 8 7 V M M V + in C 2 1 in V c out I bias C L M M M 4 6 3 1) In this case, GBW and SR are choose to be barely on the design target V ss Target: GBW=25MHz; SR=25V/us *25) g I 2*(2* = 12.56 m 1 25 D 1 g I = 12.56 m 6 2) Choosing k = 1 , then D 6 I I = 3) Choosing 0.1 D 1 Final Value will be slightly larger due to parasitic caps D 6 4) Calculate Cc=443fF C I I 0.443 2*2.443 = = = ( 0.1) ( 0.09) c + D 1 5) Checking Valid 2( C C ) D 6 L c IOWA STATE UNIVERSITY Department of Electrical and Computer Engineering

Design Step 6 gm/Id NMOS = I I 75 = A W L 6 = ( ) 38 6 1 1.97 A VEB du 6 PMOS gm/Id = I I 7.5 0.471 = A W L 1 = ( ) 16 1 1 A du 1 VEB IOWA STATE UNIVERSITY Department of Electrical and Computer Engineering

Design Step 7 & 8 V DD M3 and M4 need to have over-drive voltage in the range of 200mV to 300mV M 5 M M 8 7 For the Top three transistors M5-M7, the over-drive voltage is set to be 300mV~400mV for the purpose of reducing current mismatch, and the Vds need to be large (usually Vds>=1.5*Vod ) V M M V + in C 2 1 in V c out I bias C L M M M 4 6 3 V ss IOWA STATE UNIVERSITY Department of Electrical and Computer Engineering

Simulated Result Specs Specification Simulation Supply Voltages +/- 2.5V +/-2.5V Total Current <=100uA 90uA DC Gain 75dB 77dB Gain-bandwidth-product 25MHz 25MHz Phase Margin 60 61 Slew Rate: SR+/- 25MV/s 22.37/25.9 MV/s The design is essentially right on the target without any tweaking IOWA STATE UNIVERSITY Department of Electrical and Computer Engineering

Loop Stability Simulation Using stb analysis in close-loop V=0 IOWA STATE UNIVERSITY Department of Electrical and Computer Engineering

Slew Rate Simulation IOWA STATE UNIVERSITY Department of Electrical and Computer Engineering

Conclusion The key advantage of gm/Id based design is that it allows you to transition from hand analysis to Spice simulation without much of modelling uncertainties - Because we incorporating the relevant simulation data into into the design process. The simulation result of gm/Id based design can match the fabricated circuit well - Because the gm/id directly carries on the device measurement information IOWA STATE UNIVERSITY Department of Electrical and Computer Engineering

Questions? Thank you for your attention IOWA STATE UNIVERSITY Department of Electrical and Computer Engineering