Branch Datapath and Control Unit Design for RISC-V Single-Cycle Processor

Explore the design and implementation of the branch datapath and complete control unit for a RISC-V single-cycle processor. Learn about branching, beq instruction evaluation, ImmGen circuit operation, and connecting the branch datapath with instruction fetch datapath. Dive into the details of register-ALU datapath, memory access datapath, and the overall control unit design. Practice writing RISC-V versions of C code and enhance your understanding of processor architecture.

Download Presentation

Please find below an Image/Link to download the presentation.

The content on the website is provided AS IS for your information and personal use only. It may not be sold, licensed, or shared on other websites without obtaining consent from the author.If you encounter any issues during the download, it is possible that the publisher has removed the file from their server.

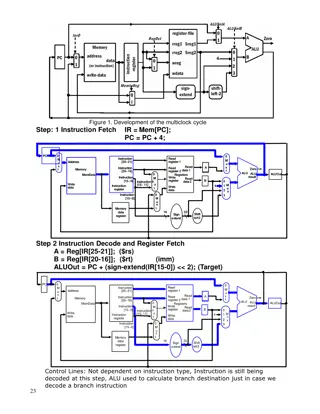

You are allowed to download the files provided on this website for personal or commercial use, subject to the condition that they are used lawfully. All files are the property of their respective owners.

The content on the website is provided AS IS for your information and personal use only. It may not be sold, licensed, or shared on other websites without obtaining consent from the author.

E N D

Presentation Transcript

Branch Datapath and Complete Control Unit CS3432 Fall 2020 Shirley Moore, Instructor svmoore@utep.edu November 5, 2020 1

Schedule for Todays Class Announcements Make appointments to discuss midterm exam at https://calendly.com/svmoore (choose 15 or 30 minute appointment) Midterm retake exams (3 parts) will be ready hopefully tomorrow Drop deadline extended to December 3, drops this semester will not count towards 6 course drop limit; no decision yet on S/U grading option COVID-related extensions Will send announcement for survey about Lab 3 Quiz next week on memory design Finish Example 3 pointer problem (5-10 minutes) Branch datapath (20 minutes) Combined branch and instruction fetch datapath (20 minutes) Control unit (10 min) Wrapup 2

Example 3 - C version // Remove value from list pointed to by head. struct node *head, *current, *prev; if (head != NULL) { prev = head; if (head->val == value) { head = head->next; free(prev); } else { current = prev->next; while (current != NULL && current->val != value) { prev = current; current = current->next; } if (current != NULL) { prev->next = current->next; free(current); } } } Try to write RISC-V version for this class. Assume we can call a procedure named free that takes an address and the number of bytes to free as arguments and returns 0 if successful and -1 otherwise. 3

Single-cycle Processor For Lab3, you are focusing on the register-ALU datapath for arithmetic-logical instructions. Last class we focused on two parts of the overall datapath: The instruction fetch datapath The memory access datapath This class we will add branching and design the complete control unit. 4

Datapath for branch instructions The only branch instruction in our RISC-V subset is beq. e.g., beq x5, x6, next 0x00628463 00000000011000101000010001100011 0 000000 00110 00101 000 0100 0 1100011 Use the ALU to evaluate the branch condition (How?) ImmGen circuit needs to generate a 64-bit sign extended output from the immediate fields for the I, S, and SB format instructions. Can also do Shift left 1 in ImmGen Compute branch target by adding immediate value to current PC. Connect branch datapath with instruction fetch datapath from last class 5

Recall instruction formats R format: add, sub, and, or I format: addi, andi, ori, ld S format: sd SB format: beq Why is the imm field split into parts in the S and SB formats? 6

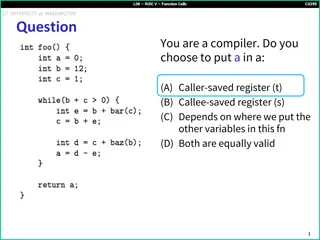

Design ImmGen circuit to map I, S, and SB imm fields to sign-extended imm64 inst[6] inst[5] imm[0] 0 0 inst[20] 0 1 inst[7] 1 1 0 64-bit immediates produced, imm[63:0] 63 Need multiplexers to make decisions for imm[0], imm[4-1], imm[11] 7

ImmGen Multiplexers Which instruction bits should we use as select bits for the multiplexers? Instruction Format Opcode addi, andi, ori, ld I 0010011, 0000011 sd S 0100011 beq SB 1100011 inst[6] inst[5] imm[0] inst[5] imm[4-1] inst[6] imm[11] Let s build these multiplexers in Logisim. 0 0 inst[20] 0 inst[24-21] 0 inst[31] 0 1 inst[7] 1 inst[11-8] 1 inst[7] 1 1 0 Then let s put it all together to build the ImmGen circuit in Logisim. 8

Now lets build the branch datapath Logisim demo: branch_datapath.circ The is demo is using the Arithmetic/Comparator rather than your 64-bit ALU; you should use your 64-bit ALU with the ALUctrl set appropriately. Test case beq x5, x6, next 0x00628463 00000000011000101000010001100011 0 000000 00110 00101 000 0100 0 1100011 9

Now lets connect the instruction fetch and branch datapaths Logisim demo: instpath2.circ, branch.txt This is NOT how you will connect them for the entire processor. We are connecting them together for the purpose of testing. 10

Control Unit for RISC-V Subset Figure 4.21 11

Truth Table for Control Unit Figure 4.22 This table does not include control for arithmetic immediate instructions. You will need to add that for Lab 4. 12