Verilog Guideline for Better Coding Practices

Explore the fundamental Verilog guidelines for improving your coding style. Learn about combinational loops, hierarchical design, D flip-flops, concise sequential blocks, multiple drivers, and more. Avoid common mistakes and enhance the readability and efficiency of your Verilog code.

Download Presentation

Please find below an Image/Link to download the presentation.

The content on the website is provided AS IS for your information and personal use only. It may not be sold, licensed, or shared on other websites without obtaining consent from the author. If you encounter any issues during the download, it is possible that the publisher has removed the file from their server.

You are allowed to download the files provided on this website for personal or commercial use, subject to the condition that they are used lawfully. All files are the property of their respective owners.

The content on the website is provided AS IS for your information and personal use only. It may not be sold, licensed, or shared on other websites without obtaining consent from the author.

E N D

Presentation Transcript

Verilog guideline Date : 3/16 CW Chu 1

Background Given some of you have same defective and wrong coding style, this ppt will introduce some useful concepts and talk about fundamental Verilog guideline. If there are any questions, please let us know. RED are wrong example which you should avoid. GREEN are good example which you should learn. 2

Outline 1. Combinational loop 2. Hierarchical design 3. D flip-flop 4. Concise sequential block 5. Multiple driver 6. Bit truncation 7. Good naming 8. Avoid latch warning 3

Combinational loop always@* begin value_next = value_next + 1'd1; end For software, a=a+1 means a plus 1 and save back. always@(posedge clk or negedge rst_n) if(~rst_n) value <= 4'd0; else value <= value_next; For hardware, every signals are voltage . there is no situation that a signal will equal to itself plus a high voltage. 4

Hierarchical design Module call is a useful function to add original design to a new design. DO NOT copy the code to your new design directly, it will make your code awful and hard to read. ex Counter U_counter_digit1( .clk(clk), .rst_n(rst_n), .value(out) ); Try to make the top module more concise, only module call and wire connection if you can. More specific module separation, easier debugging. 5

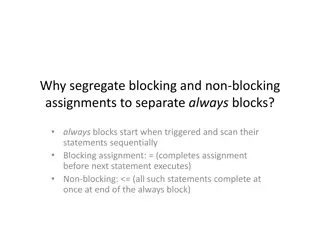

D flip-flop always@ (posedge clk or negedge rst_n) For asynchronous reset design, you should base on clk and rst_n only. If there are other signals in the bracket, the synthesized circuit may not be D flip-flop. Remember <= not = 6

Concise sequential block always@* begin value_next = value + 1'd1; end Make the sequential block only has reset and update value, no more if else keyword or other logic calculation. always@(posedge clk or negedge rst_n) if(~rst_n) value <= 4'd0; else value <= value_next; In this case, we only need to concern value_next operation in other block. 7

Multiple driver always@* begin q = .... ... .... end // block 1 always@* begin q = .... ... .... end always@* begin .... q = .... ... .... end // block 2 8

Multiple driver For software programing, you can change a variable in different function. For Verilog, always block is the behavior description not a function. Any behaviors are synthesized circuit, so you can t drive a signal by different driving circuits. 9

Bit truncation wire out; // 1 bit When calling module, you should check that the bit of wire is consistent to module IO. Counter U_counter_digit1( .clk(clk), .rst_n(rst_n), .value(out) ); // 4-bits value // four bit signal connect to one bit signal. 10

Good naming reg a, aa, b, cc, d; Every naming need to be clear, use underline(_) to make it more specific. reg in_1, value_out, value_next; It will help you in this course or other programing project. 11

Avoid latch warning always@* begin if (a=1'd0) begin b_next=1; c_next=1; end always@* begin if (a=1'd0) begin b_next=1; c_next=1; end else begin b_next=0; c_next=c; end end else b_next=0; end 12

Avoid latch warning You should cover all case if there are if else or case operation. In the statement(if or else if or case), every behaviors of the reg, which belongs to the block should be specific. There is another method to avoid latch by more concise coding, if you are interested in it, please let me know. 13

Conclusion This ppt only includes a part of coding style guideline, other concepts might be introduce in future lab. Thinking, drawing block diagram and integrating design concept before coding. Practice makes perfect, remember the guideline and keeping coding. 14